| LCFI                        |                                  |     |

|-----------------------------|----------------------------------|-----|

|                             |                                  | PPd |

| 120-<br>110-<br>100-        |                                  |     |

|                             |                                  |     |

|                             | <b>LCFI</b> Collaboration        |     |

|                             | <b>Status Report</b>             |     |

|                             |                                  |     |

|                             | Paris                            |     |

|                             | Joel Goldstein                   |     |

| Reisto                      | for the LCFI Collaboration       |     |

| FPGA 1 Test Output 1 1 Test | ol, Lancaster, Liverpool, Oxfore |     |

|                             |                                  |     |

### **R&D** for a vertex detector at NLC or TESLA

1. Physics Studies

(See Sonja Hillert's talk in Simulation session)

- 2. Mechanical Development

- Ultra low-mass ladders

- FEA/physical models

- **3. Detector Development**

- **Fast CCD technology** (50 MHz for TESLA)

- Custom CMOS readout chips

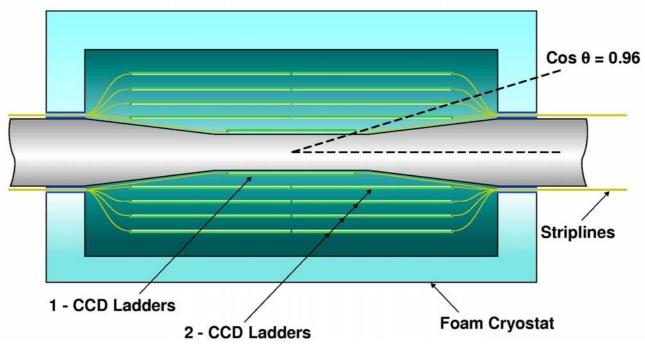

## **LC Vertex Detector**

- 800 Mchannels of 20×20 µm pixels in 5 layers

- Optimisation:

- Inner radius (1.5 cm?)

- Readout time  $(50 \ \mu s?)$

- Ladder thickness  $(0.1\% X_0?)$

Joel Goldstein, RAL

LCFI

Q\_X

# **Mechanical Options**

# **Target of 0.1% X<sub>0</sub> per layer** (100μm silicon equivalent)

- 1. Unsupported Silicon

- Longitudinal tensioning provides stiffness

- No lateral stability

- Not believed to be promising

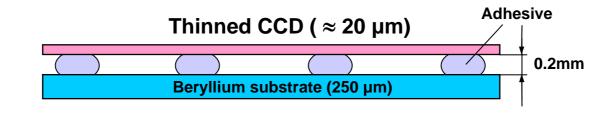

### 2. Semi-supported Ultra-thin Silicon

- Detector thinned to epitaxial layer (20μm)

- Silicon glued to low mass substrate for lateral stability

- Beryllium has best specific stiffness

- Composites, ceramics, foams...

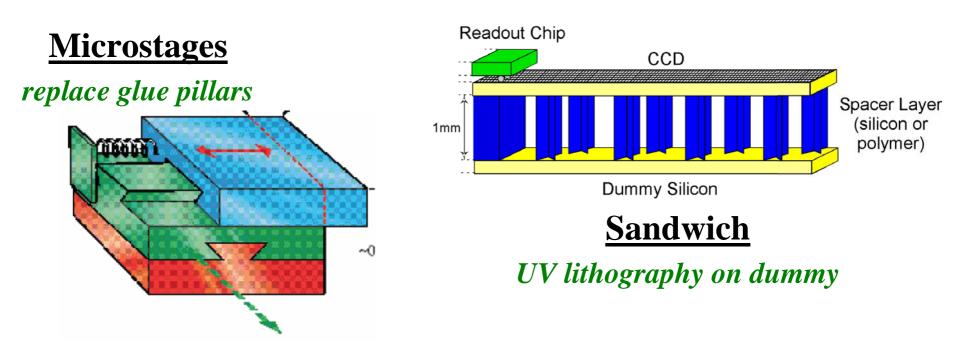

### 3. Novel Structures

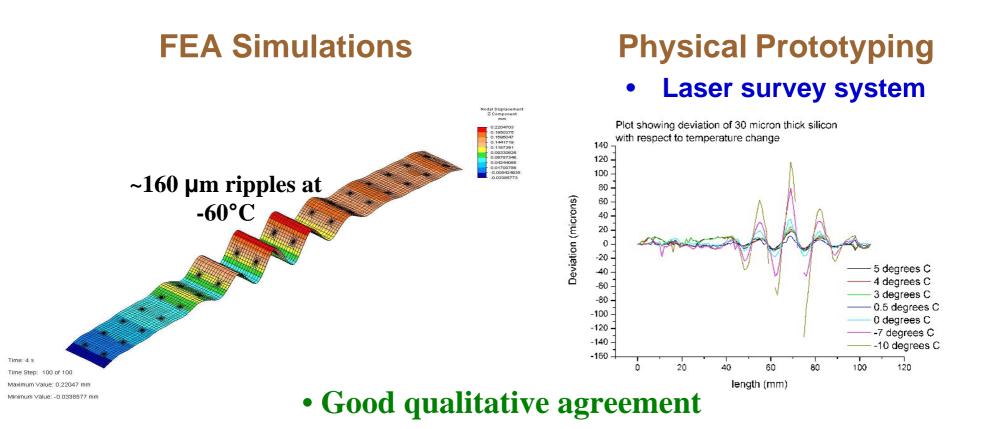

### **Mechanical Studies of Be-Si**

Joel Goldstein, RAL

LCFI

Q\_X

# **New Approaches**

- Be-Si unstable when cooled due to CTE mismatch

- Choose substrate with closer CTE match

- 100  $\mu m$  carbon fibre

- ceramic foam

- Micromechanical techniques....

Joel Goldstein, RAL

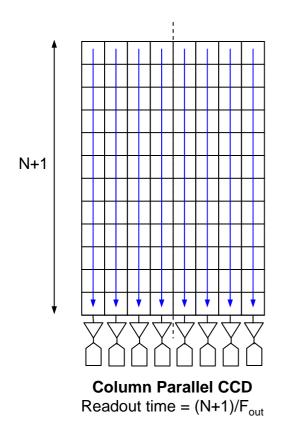

# **Column Parallel CCD**

• Separate amplifier and readout for each column

### **CPC1 produced by E2V**

- **Two phase operation**

- **Metal strapping for clock**

- 2 different gate shapes

- **3 different types of output**

- 2 different implant levels

Clock with highest frequency at lowest voltage

CFI

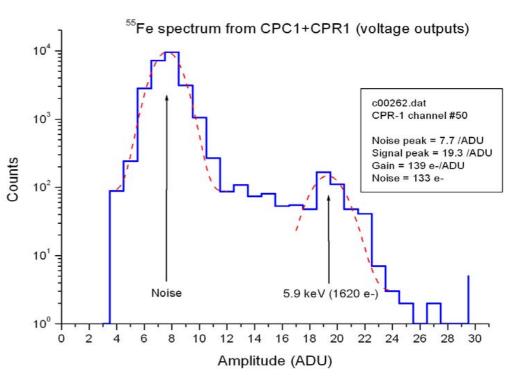

Noise ~ 100 electrons 10000 (60 after filter) Raw ADC data at 1 MHz  $\sigma_{noise}$  = 3.92 ADC channels (62 electrons) 1000 Minimum clock ~1.9 V Counts 100 10 160 -O- CTI vs Clock Amplitude 140 CPC-1 at -50 °C, 500 kHz 120 Reset every pixel -50 -25 125 150 175 200 225 0 25 50 75 100 250 100 CTI (×10<sup>-5</sup>) ADC channel 80 Minimum clock amplitude  $\approx 2 V_{or}$ 60 Maximum frequency > 25 MHz • 40 20 – inherent clock asymmetry

2.5

3.0

3.5

Clock amplitude (Vpp)

4.5

5.0

4.0

5.5

2.0

0

1.5

Joel Goldstein, RAL

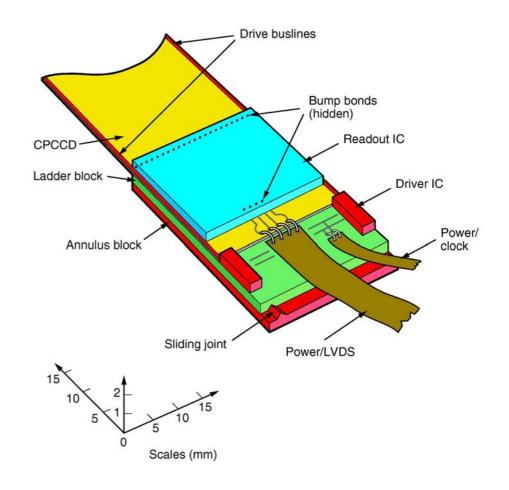

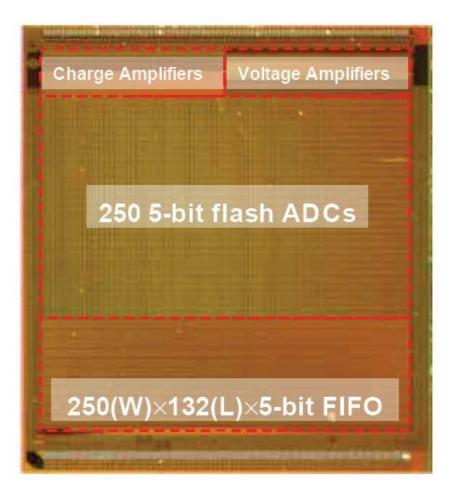

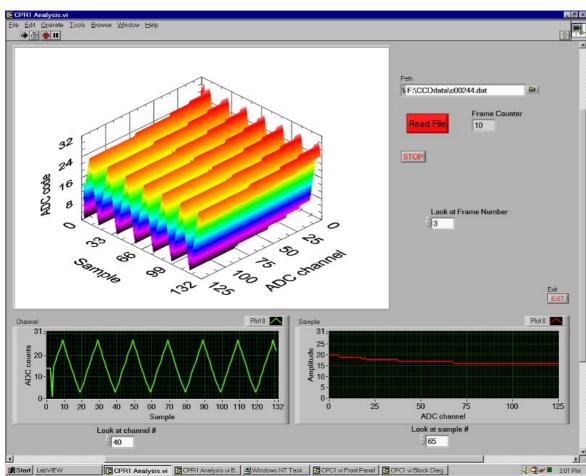

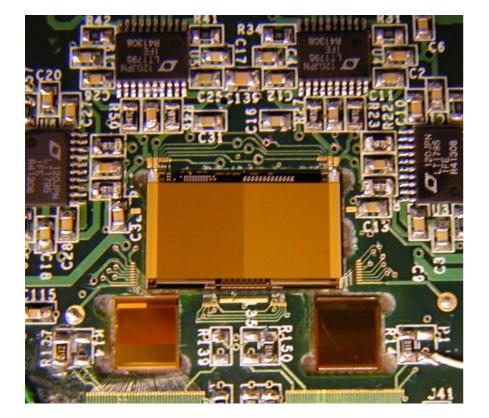

### **CP Readout ASIC**

### **CPR1** designed by **RAL** ME Group

- IBM 0.25 µm process

- 250 parallel channels with 20µm pitch

- Designed for 50 MHz

- Data multiplexed out through 2 pads

# **CPR1** Testing

### Voltage injection into ADC

- Flash ADCs tested

- Voltage and charge amplifiers tested

- Voltage gain ~40

- Very sensitive to timing and bias values

- Outstanding digital problems

- Charge amplifiers not fully understood

### **Bump bonding underway at VTT**

- Total noise ~130 electrons

- Noise from preamps negligible

Joel Goldstein, RAL

LCFI

- Test Programme

- Bump bonded assemblies expected early May

- Radiation effects on fast CCDs

- High frequency clocking

- Next Generation CCDs and ASIC

- Detector scale CCDs

- Cluster finding logic

- Design underway; production later in year

- In-situ Storage Devices

- Resistant to RF interference

- Reduced clocking requirements

(See Chris Damerell's talk on Thursday)

LCFI

- Excellent progress over past two years

- Mechanical options studied in detail

- CCD+ASIC operation achieved

- New ideas being discussed

- CP CCDs are viable technology for linear collider

- Next generation will be full-scale prototype CCDs

- > Accelerator technology choice will determine path