# Strategies for pickup and noise suppression with different vertex detector technologies

#### **Chris Damerell**

#### On behalf of the LCFI collaboration

□ The challenge at TESLA: 109 tiny signals (~1000 e-) needing to be amplified purely electronically and read in conditions of severe beam-related RF pickup

□ Reality check: 300 Mpixels at SLD

□ Detector at NLC (natural evolution from SLD)

□ Detector at TESLA

□ Last December we thought of a possible solution (thanks to Renato Turchetta and David Burt for valuable discussions)

□ We recently found that it isn't a new idea at all, and many of our requirements have been established. ISIS (Image Sensor with In-Situ Storage) looks extremely promising

- ☐ A Linear Collider is intrinsically more hostile in terms of beamrelated RF than storage rings. Why?

- Collimators, beampipe irregularities, BPMs, position monitors can be much more disruptive, due to single pass operation

- Due to requirement of nm spots, invasive diagnostic tools are essential. Imperfections in shielding of cables, optical ports, ...

- □ Vertex detector is more vulnerable to pickup than others. Why?

- Intimately enmeshed with beampipe Faraday cage ideals tend to be compromised

- Tiny signals from thin silicon active layers (~1000 e-) with need for purely electronic amplification

- SLD experience: massive pickup observed, and optical transmission was disrupted by every bunch took tens of  $\mu s$  to recover

- However, a readout strategy was developed that worked ...

#### **Ideal CCD:**

#### Readout at Linear Collider during bunch train:

Malos's first rule of electronics: 'There is no such thing as ground ... Why whisper just when an express train roars through the station?

#### SLD approach:

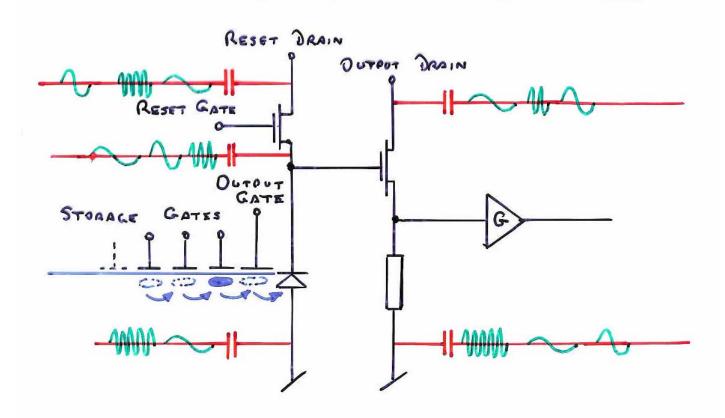

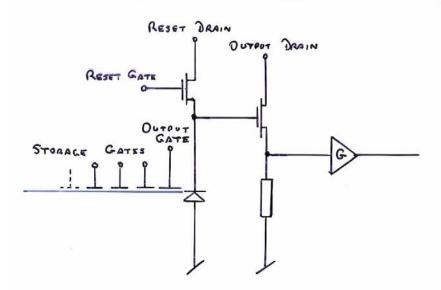

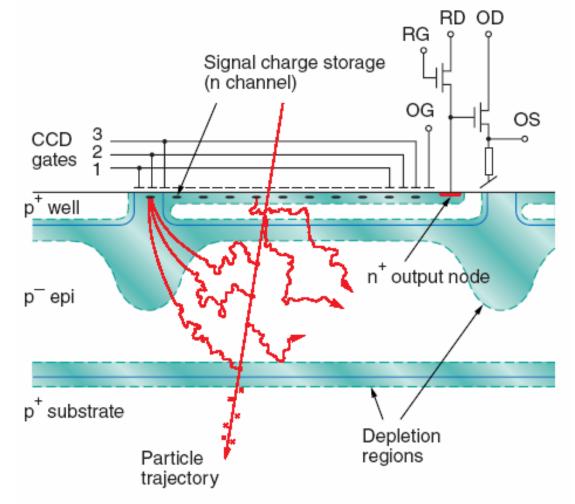

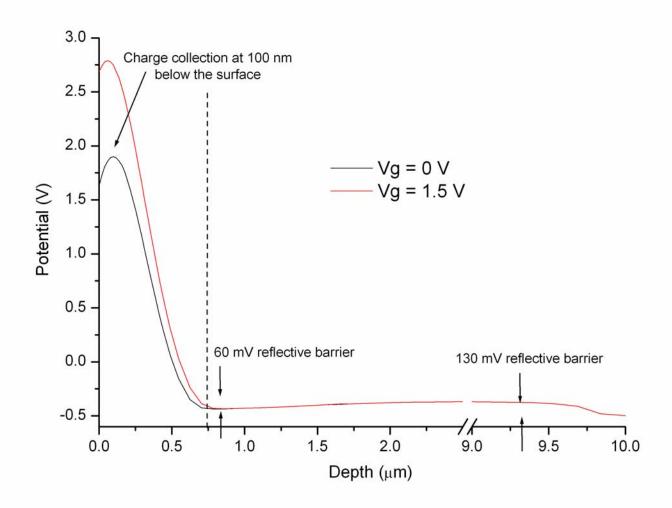

- During bunch train, signal charge from MIP is stored safely in buried channel of the device (~10° greater pickup immunity than output cct)

- Only long afterwards, when pickup has died down, is charge transferred to output node and sensed as voltage on the gate of the output transistor. Even then, it is important to suppress pickup from non-beam sources ...

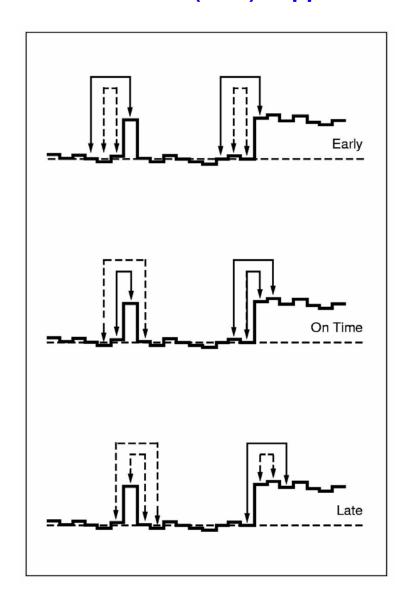

- Classical Correlated Double Sampling (CDS):

RESET/READ 1/TRANSFER/READ 2 (originally to suppress reset noise)

• Sparse data scenario permits faster (but equivalent) noise suppression:

RESET/READ 1/TRANSFER/READ 2/TRANSFER/READ 3/ ...

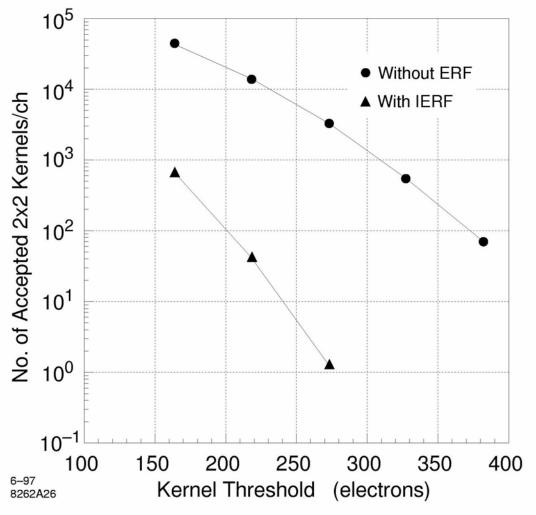

#### **Extended Row Filter (ERF) suppresses residual pickup:**

#### **SLD** experience:

Without ERF, rate of trigger pixels would have deluged the DAQ system

Read out at 5 MHz, during 'quiet' inter-bunch periods of 8 ms duration

Origin of the pickup spikes? We have no idea, but not surprising given the electronic activity, reading out other detectors, etc

### In-situ storage of signal charge: a new architecture for TESLA

- Strategy of reading inner layer 20 times during the train is now considered to be suspect

- Simulation is impossible at least according to all RF experts we have consulted

- Idea of 'final focus lab' has been proposed, but regarded with great scepticism everything depends on minor details. Under pressure of the real installation process, these details will not be precisely replicated

- If there are problems, diagnosis is almost impossible. Can only run beams with the detector closed

- So we looked for a solution which avoids multiple readout of voltage signals wait till the express trains have long ago disappeared into the beam dumps!

- Secret may lie in the robust storage of charge in a buried channel, which cannot be disrupted even by massive pickup to the clocking gates or to ground

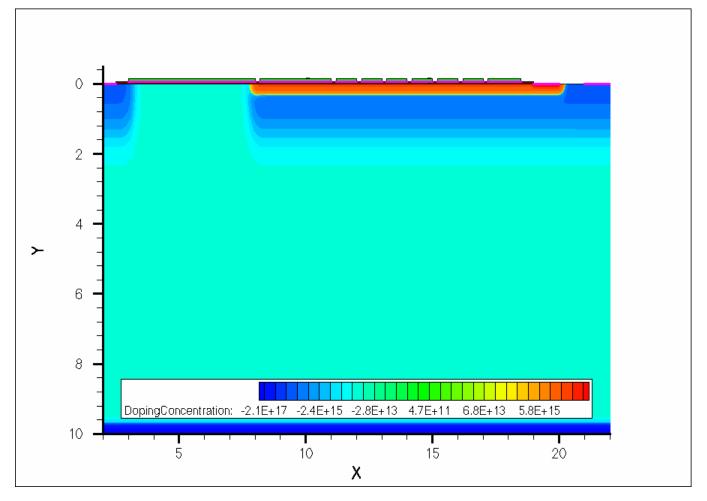

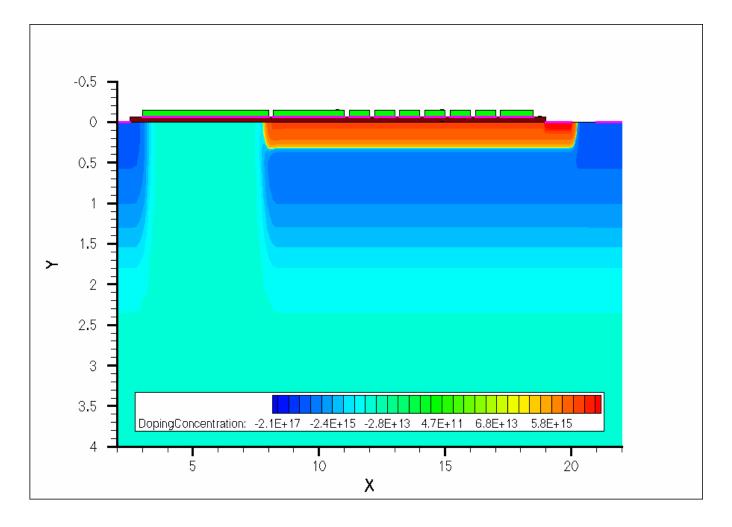

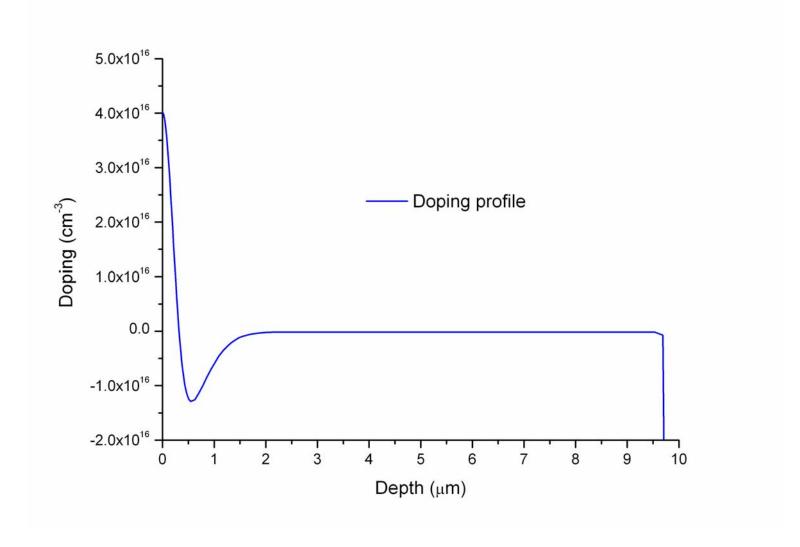

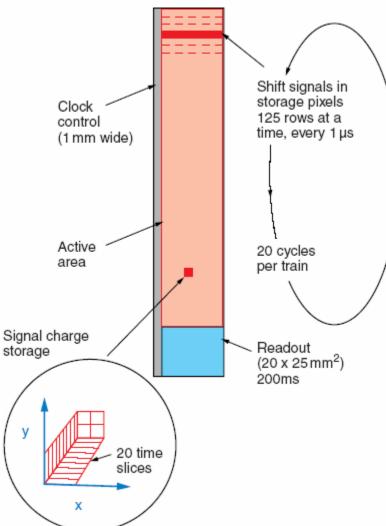

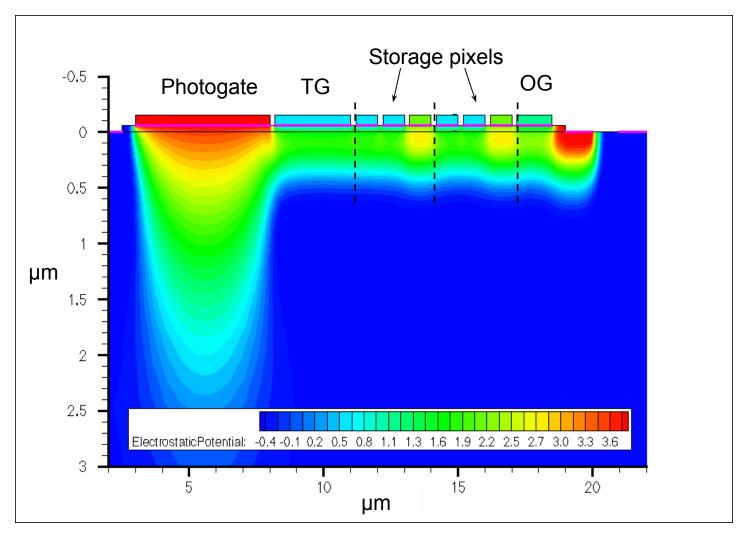

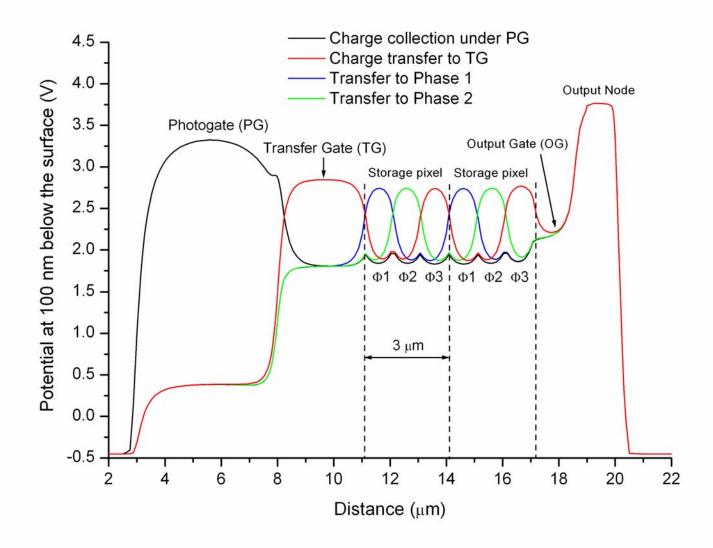

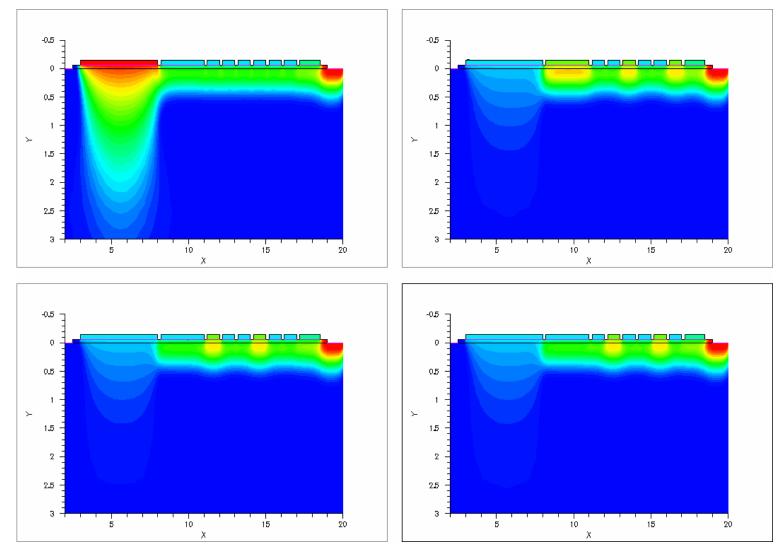

- Strategy is to transfer signal charge from photogate to a linear register inside each pixel, at intervals of 50  $\mu$ s

- charge collection to photogate from 20-30  $\mu m$  silicon, as in a conventional CCD

- signal charge shifted into storage register every  $50\mu s$ , to provide required time slicing

- string of signal charges is stored during bunch train in a buried channel, completely avoiding charge-voltage conversion

- totally noise-free charge storage, ready for readout in 200 ms of calm conditions between trains

- particles which hit the storage register (~30% area) leave a small 'direct' signal (~5% MIP) totally negligible or easily corrected

# L C F I

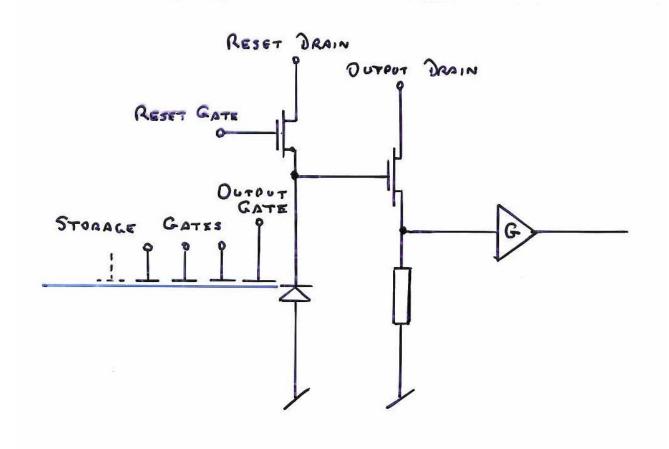

#### Pixel unit cell: practical layout

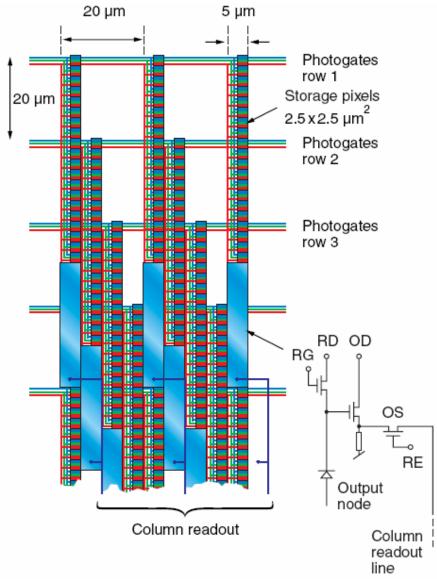

- imaging pixels on 20x20 μm² slightly trapezoidal layout

- storage register plus output circuit fits within  $5x80 = 400 \mu m^2$

- output cct is usual 3 T, plus a row enable switch to close connection to column readout busline

Active area 6250 x 1250 imaging pixels 125 x 25 mm<sup>2</sup>

- during bunch train, shift 128 rows at a time by 1 storage pixel, at relaxed frequency of 1 MHz

- cycle round active area (length 12.5 cm) every 50 μs

- at end of train, every imaging pixel contains stored signal charges for 20 time slices

- between trains, column parallel readout just as in CPCCD

- •full power of CDS and ERF in quiet inter-train period, as at SLC or NLC

- •Relaxed sampling at 1 µs per stored signal implies 125 ms for complete detector readout

- no problem to process 2\*10<sup>10</sup> signals with low noise and effective pickup suppression

- could change from 128 to 256, 512, .. rows per block, at even more relaxed frequency detailed question of optimising driver design

### Following 4 beautiful simulation slides thanks to Konstantin Stefanov and ISE-TCAD

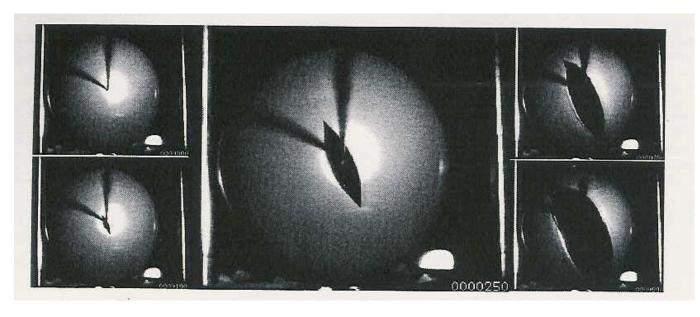

# ISIS: Imaging Sensor with In-situ Storage

- Pioneered by W F Kosonocky et al IEEE SSCC 1996, Digest of Technical Papers, p 182

- T Goji Etoh et al, IEEE ED 50 (2003) 144

- 1 Mfps, seen above running at 100 kfps (312x260 pixels) dart bursting balloon

- Evolution from 4500 fps sensor developed in 1991, which became the de facto standard high speed camera (Kodak HS4540 and Photron FASTCAM)

| Feature                   | ISIS 2003 | Goal for TESLA                                    |

|---------------------------|-----------|---------------------------------------------------|

| Particle-sensitive?       | no        | yes                                               |

| Imaging pixel size<br>μm² | 66x66     | 20x20                                             |

| Storage pixel size        | 5.1x5.1   | 2.5x2.5 *                                         |

| Frame rate                | 1 MHz     | 20 kHz                                            |

| Frames stored             | 100       | 20                                                |

| Resolution (amplitude)    | 10 bits   | 5-6 bits                                          |

| Well capacity             | 25000 e-  | 5000 e-                                           |

| Pickup immunity           | solid     | solid                                             |

| Radiation resistance      | ??        | Robust – easy to achieve 100 times standard CPCCD |

<sup>\*</sup> Kosonocky achieved 1.5x3  $\mu m^2$  BCCD storage elements in 1996 with 1.5  $\mu m$  design rules!

- Manufacture requires specific features drawn from 'standard' CCD and CMOS technology:

- 2 or 3 metal layers for horizontal and vertical tracks

- Design rules 1.5 μm or better

- large area precise stitching, of course

- Such flexibility is available in companies producing advanced imaging devices, but not 'off the shelf'

- Development being explored with e2V, DALSA Image Sensors (formerly Philips Scientific Imaging) and Sarnoff (formerly RCA)

#### **CONCLUSIONS**

| ☐ The combination of tight collimation (generating large wakefields) and instrumentation essential for a single pass collider (BPMs etc) tends to create severe RF pickup during the bunch train – already encountered at SLC, and probably more extreme at the TeV collider |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ☐ One should aim to avoid delicate voltage sensing and amplification during this period                                                                                                                                                                                      |

| ☐ ISIS - Imaging Sensor with In-situ Storage, in principle offers a solution to the problem                                                                                                                                                                                  |

| ☐ Required developments appear to be achievable, much more so than we imagined last December when we thought we had invented the idea ourselves!                                                                                                                             |

| ☐ 'Standard' CPCCD looks fine for NLC, but for TESLA we have started a serious evaluation of the ISIS architecture as a promising way forward.                                                                                                                               |

| Solves other problems with the CPCCD approach: dramatically reduced power requirements for CCD clocks, improved spatial resolution (maybe to ~1 $\mu$ m), orders of magnitude overkill in radiation hardness, near-room temperature operation,                               |