# CMS ECAL Trigger Primitives: Tests of the boards

M.Bercher, P.Busson, M.Cerutti , C.Collard, A.Debraine, L.Dobrzynski, Y.Geerebaert, J.Gilly , A.Karar, P.Paganini, N.Regnault, T.Romanteau, L.Zlatevski

## Outline

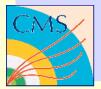

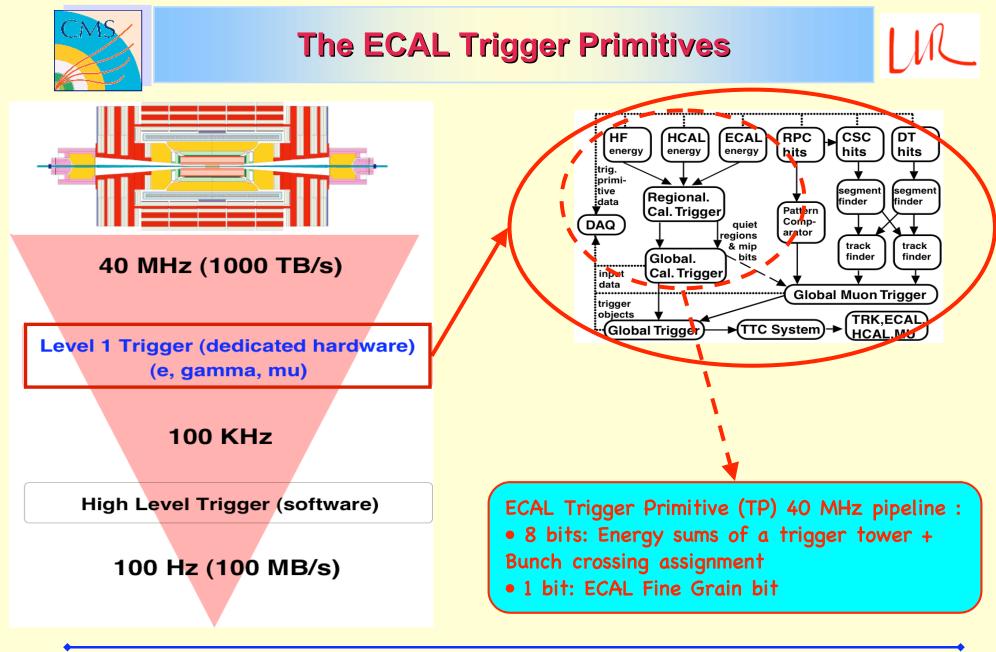

- Overview of the ECAL Trigger Primitives

- The Front-End board

- Brief overview

- XFEST: the eXtended Front-End System Test

- The Trigger Concentrator Card

- Brief overview

- TCC24: the prototype

- Tests of the TCC24

- Test bench for production

## The Front End Board

## **Brief overview of the Front End board**

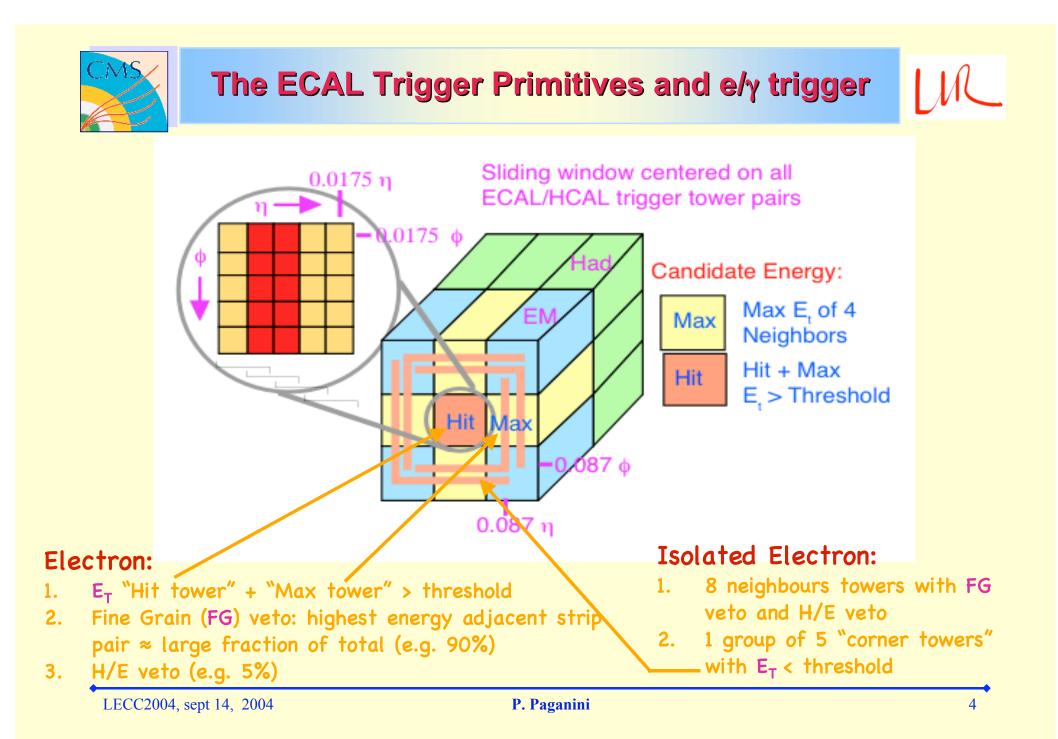

#### • The FE board:

- receives signals from a trigger tower (25 crystals of

- 5 VFE)

- stores the data during the L1 latency

- performs the Trigger Primitive calculations

- formats and sends the data (via GOH: Giga Optolink Hybrid) to the DAQ (DCC board) when L1 accept signal.

- sends the Trigger Primitives to the TCC @40 MHz (via GOH)

**GOH connectors**

**VFE connectors**

**FENIX chips**

For details, see M. Gastal's talk

10 cm

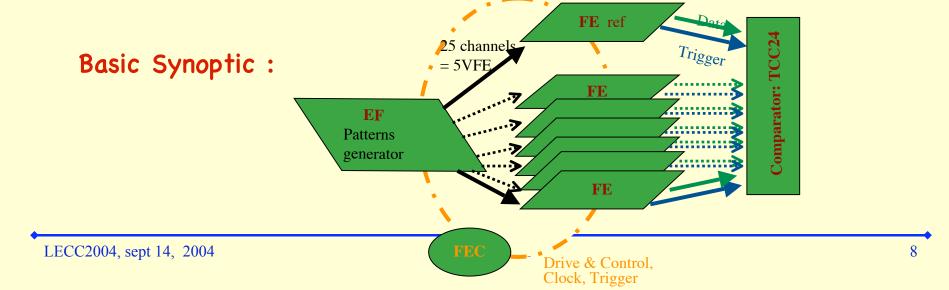

XFEST: System Test for FE board production

- 3200 boards to be tested, 80/week until mid-2005

- 1. Short tests: just after burn in to reject quickly dead boards (see M. Gastal's talk)

- 2. XFEST: Long tests (several hours) with lots of patterns

- I FE board : inputs 25 x 16 bits @ 40 MHz, outputs 2 x 800 Mbits/s ⇒ impossible to cover all patterns in a reasonable time

- Idea: inject same realistic inputs to several boards in parallel

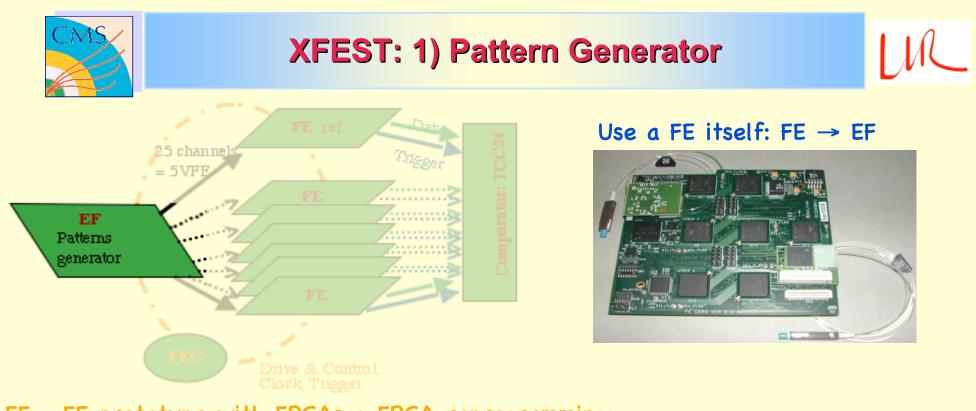

#### EF = FE prototype with FPGAs + FPGA reprogramming:

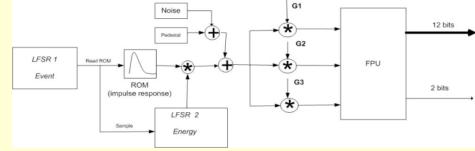

#### • Emulates signals from VFE:

- MGPA multigain

- Random noise using LFSR (40 bits)

- Variable signal amplitude using LFSR

- Allows loading of different signal shape

- Allows superposition of signals to mimic pile-up

LECC2004, sept 14, 2004

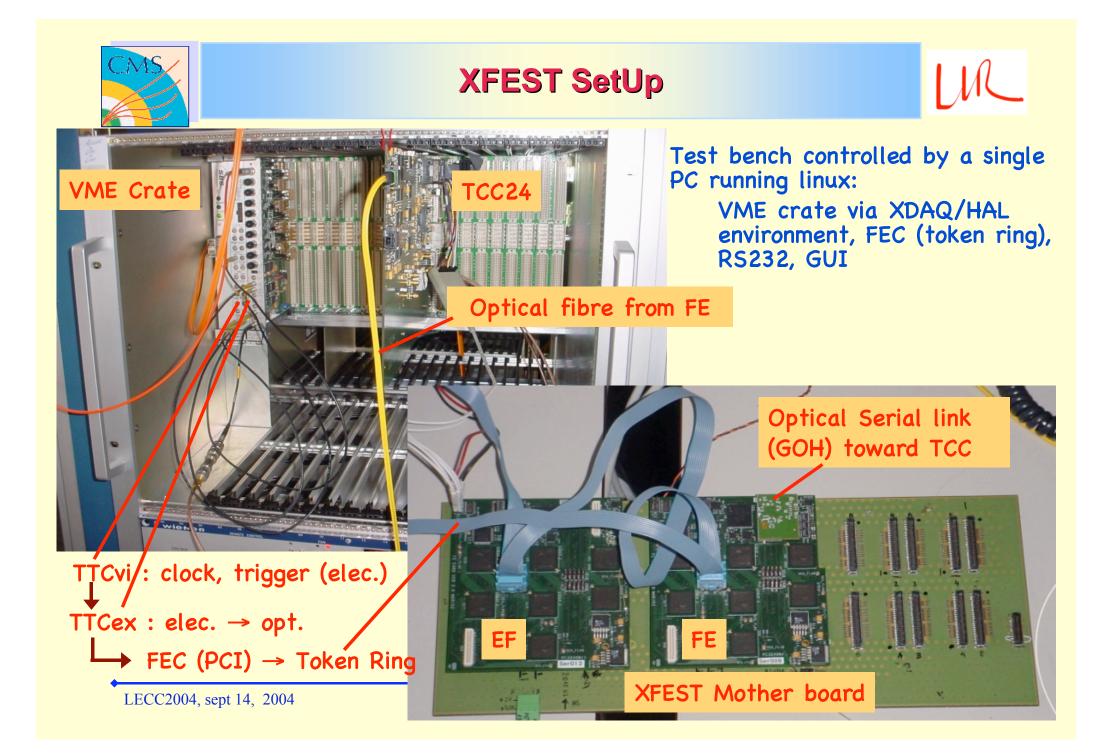

## **XFEST: 2) Mother board**

#### Mother board:

- Connect EF to several FE

- Power supply

#### Realisation of a prototype:

- EF + 2 FE

- 24 layers

- PCB class 6, 4.8 mm

# 36 cm FE1 FE2 XFEST Mother board prototype x - LLR - CHS

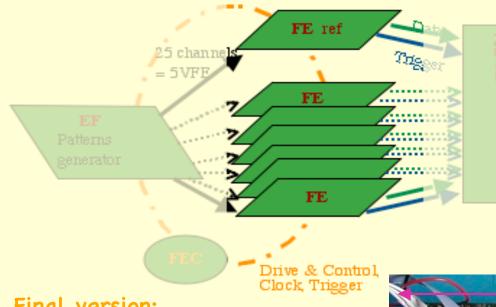

#### Final version:

• EF + 4 FE

• Strong constraints to avoid cross-talk and caution on timing of signals  $\Rightarrow$  400 traces with characteristic impedance 50  $\Omega$

- PCB class 6, 4.8mm, 48cm x 35cm

- Expected by october

P. Paganini

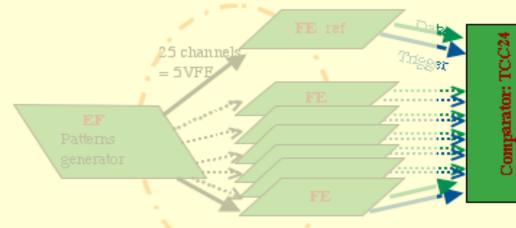

## XFEST: 3) Comparator: TCC24

#### In CMS:

- FE trigger  $\rightarrow$  TCC board

- FE Data  $\rightarrow$  DCC board

#### In XFEST:

- FE trigger+Data  $\rightarrow$  TCC board

- $\Rightarrow$  need reprogramming of TCC

#### Reprogramming allows:

- comparison of an input signal (1 FE) to other inputs

- If discrepancy, send channels in error to VME

LECC2004, sept 14, 2004

## The Trigger Concentrator Card

## Brief overview of the Trigger Concentrator Card (TCC)

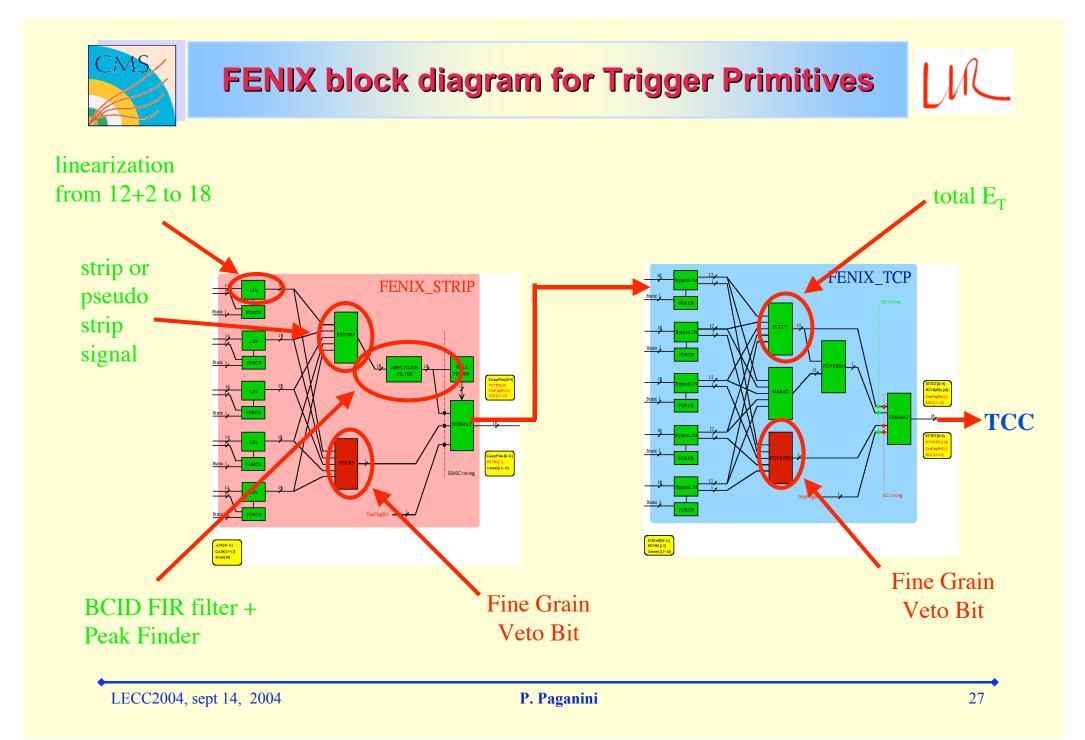

**TCC Functions :**

• Receives and deserializes the (optical) data from FE

• Finalises and encodes the Trigger Primitive (TP) using a non-linear scale for the total transverse energy

• Sends the encoded TP @ 40 MHz to the regional trigger through SLB (assuring time alignment between channels, see N. Almeida talk tomorrow)

• Stores the encoded TP during L1 latency and transmits it to DCC when L1A

• Computes TTF (= Trigger Tower Flags): Classifies trigger towers into high/medium/low interest and sends it to SRP when L1A TCC in numbers (barrel version) :

double width VME 9U module managing 72 channels (=68 trigger towers + 4 not used) ⇒ 1 whole supermodule

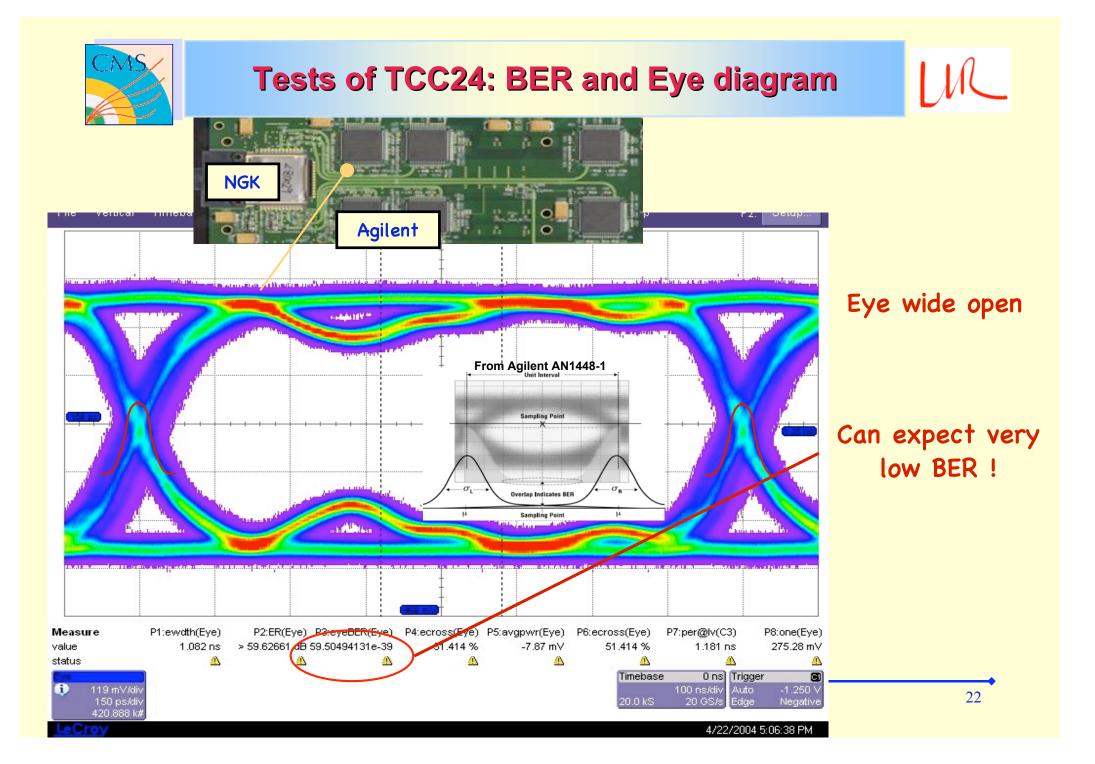

Basic Components : 6 NGKs (O/E receivers 12 channels), 72 Agilent (deserializer) and 8 FPGAs (6 Xilinx virtex2, 1 Xilinx virtex2 pro, 1 Altera) + 9 SLBs boards

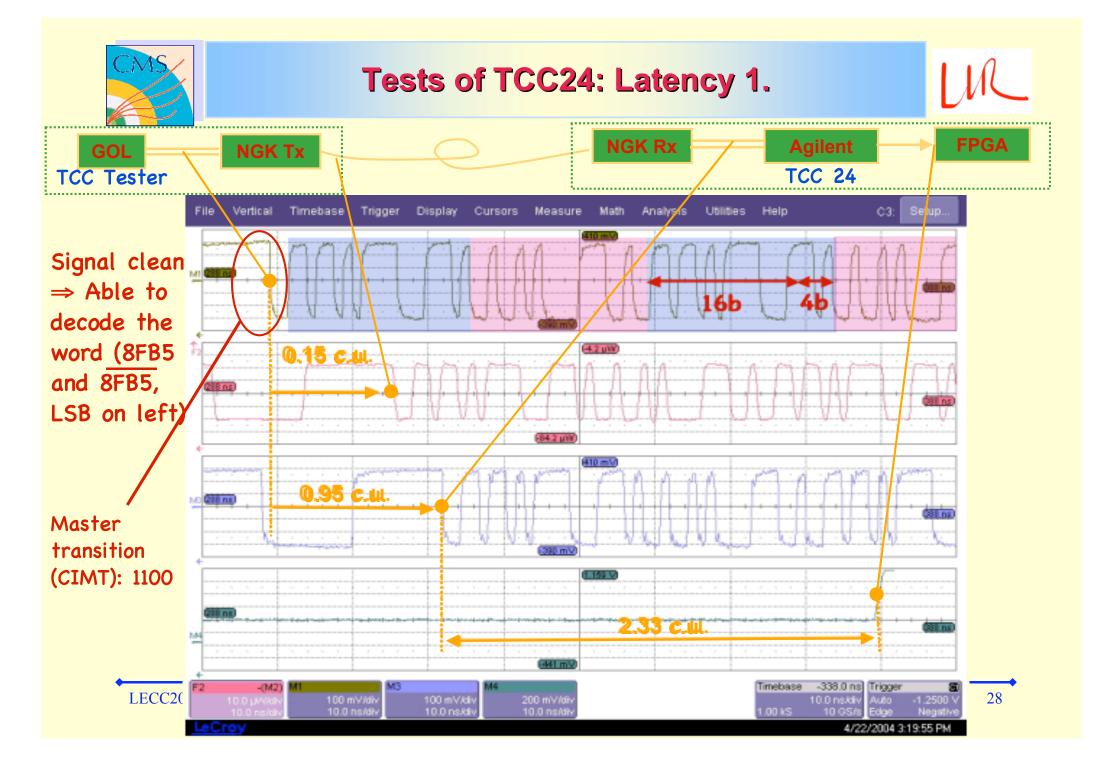

• Latency <u>must be</u>  $\leq$  7 Clocks  $\Rightarrow$ imposes Agilent choice with protocol CIMT (2.5 clocks)

LECC2004, sept 14, 2004

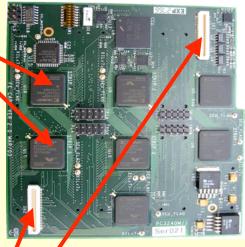

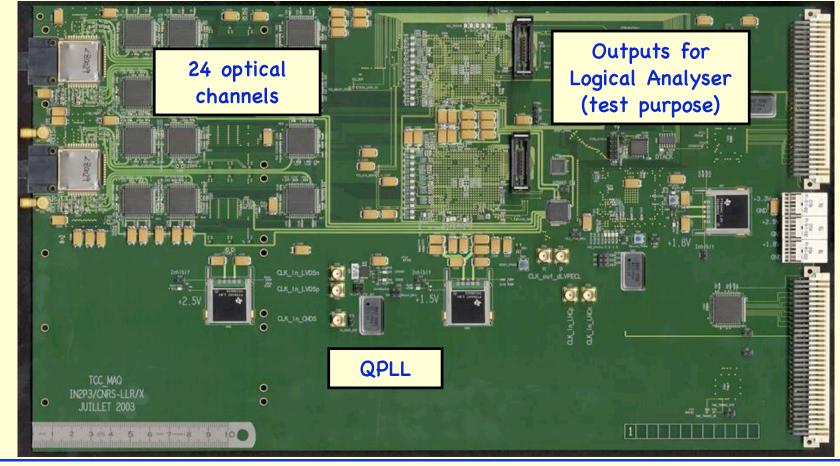

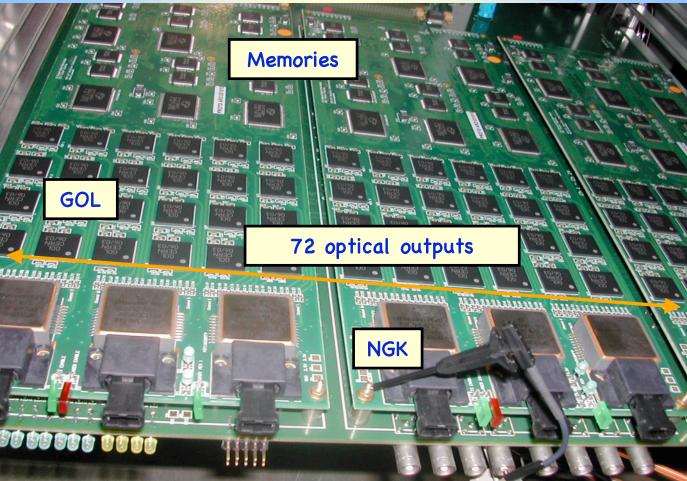

## **TCC24: Prototype top view**

Aims : validate the design/implementation: Agilent deserializers,  $\mu$ -vias, BGA TCC24 : VME 6U board, 24 channels 1/3 of final version

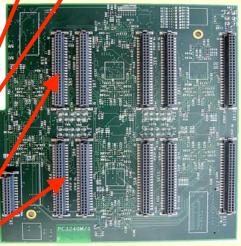

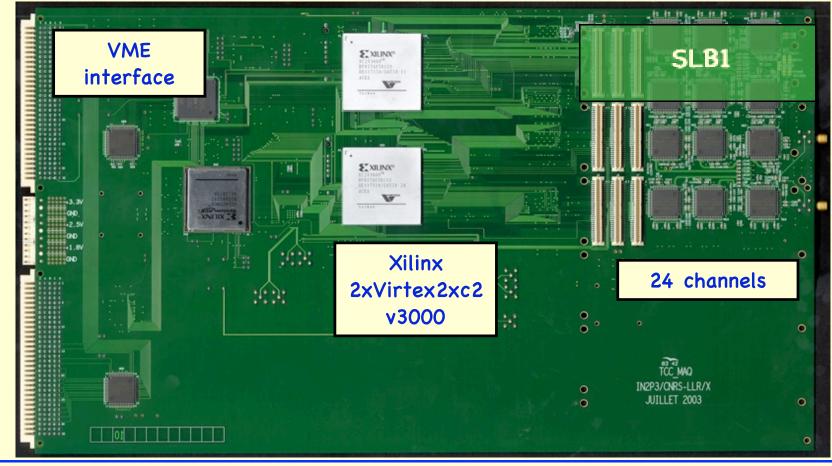

## **TCC24: Prototype bottom view**

Aims : validate the design/implementation: Agilent deserializers,  $\mu$ -vias, BGA TCC24 : VME 6U board, 24 channels 1/3 of final version

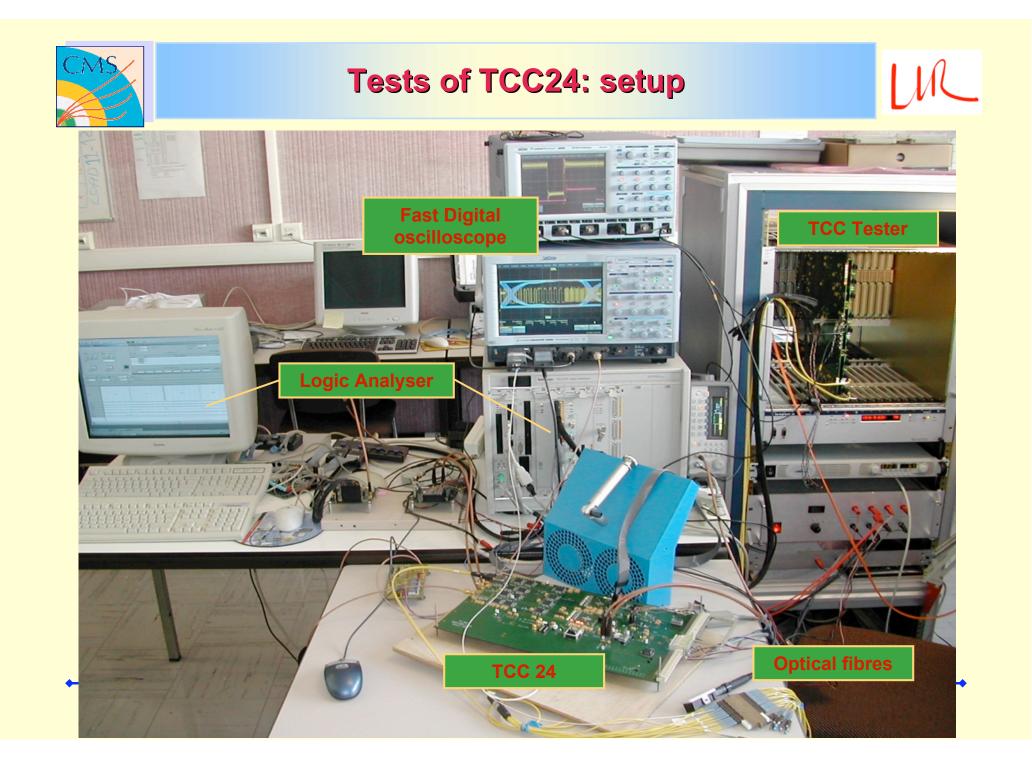

## **Tests of TCC24**

#### Tests performed :

- 1. Power consumption measurement (not shown in this talk)

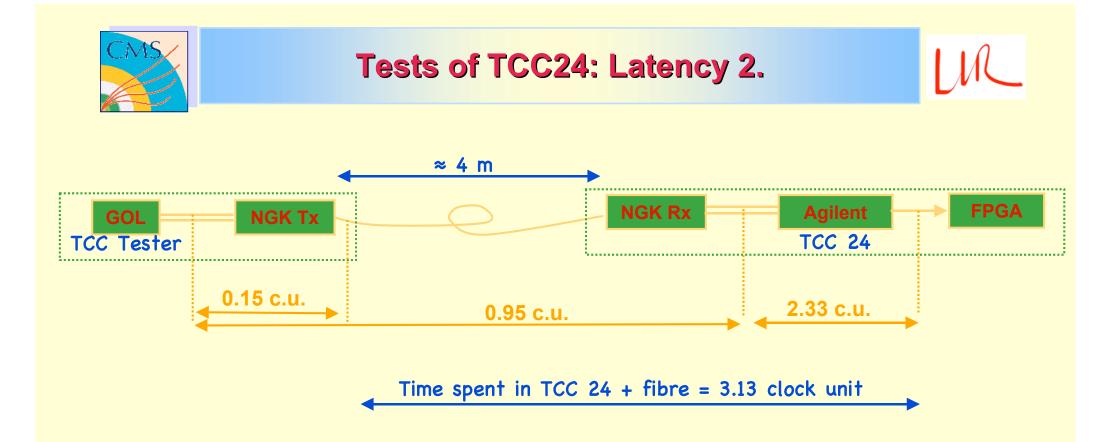

- 2. Latency measurements (not shown in this talk) : < 6 clock unit (< requirement)

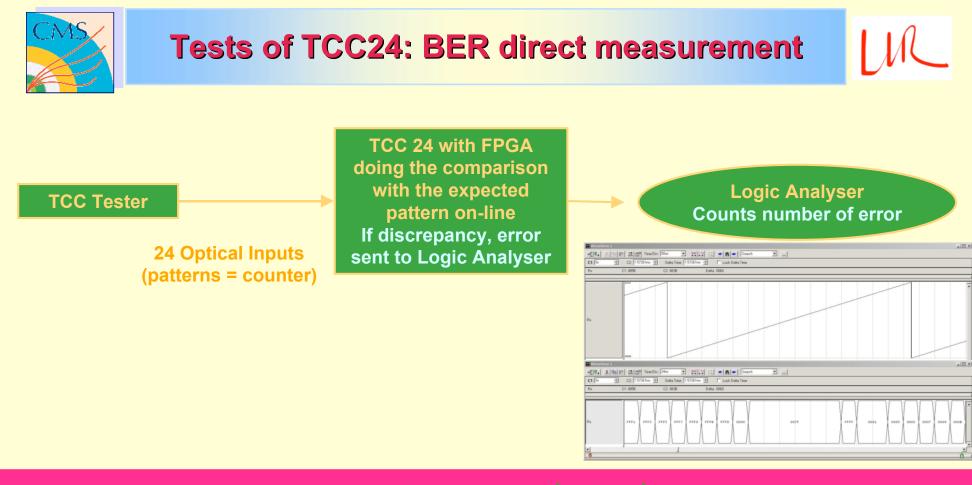

- 3. Bit Error Rate measurements

- 1. Direct measurement

- 2. Indirect measurements :

- 1. Eye diagram

- 2. Jitter

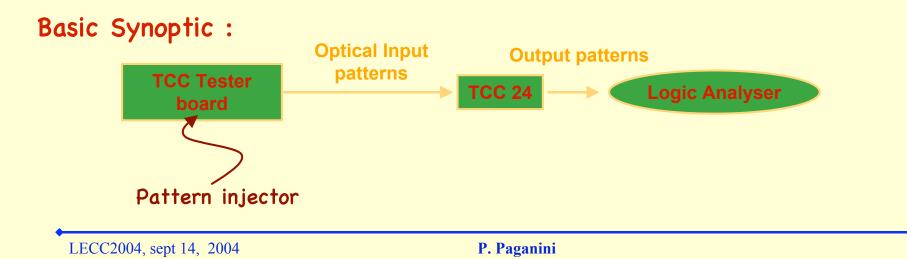

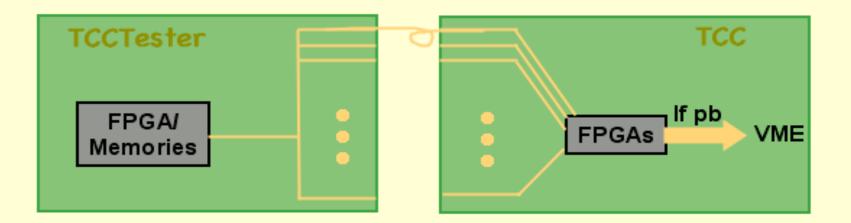

### **Tests of TCC24: TCCTester board**

TCC Tester will be used for production test bench

- TCC Tester = clone of the DCC Tester (see J. C. Da Silva talk for details)

- Able to transmit loaded pattern (in memories) @ 40 MHz

- Test continuously 1 channel during 145h (6 days) @ 40 MHz with 0 error → BER < 3.10<sup>-15</sup> → less than 1 error every 1'35" in CMS

- Test 18 channels (/24) in parallel (same pattern injected in every channel): no error during 16h10' @ 40 MHz ⇒ BER < 2.10<sup>-14</sup>

First TCC barrel in october 2004, pre-production beginning of 2005, 42 boards (barrel version) to produce/test in second half of 2005

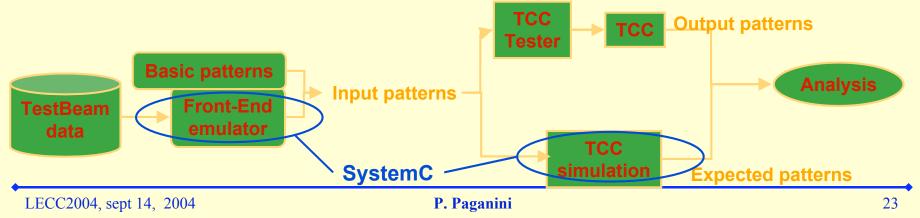

- 1. JTAG for boundary scan (up to SLB boards)

- 2. Built-in self test  $\Rightarrow$  check firmware:

- 1. patterns auto generated by TCC

- 2. Comparison to expected data in ROM

- 3. Short tests (fraction of seconds @40 MHz):

- 1. Inject patterns (coming from testbeam, counter etc)

- 2. Compare output to SystemC simulation (detailed hardware simulation, see <u>http://www.systemc.org</u> for details)

$\Rightarrow$  Uses Logic Analyser to read out/store output data

## **TCC Tests for production**

- 4. Long tests (several hours/days):

- 1. Inject

- 1. pseudo-random patterns auto generated by TCCTester

- 2. patterns loaded in TCCTester memories

- 2. Same patterns injected in <u>all channels</u>

- 3. Compare outputs in TCC FPGA itself

- 4. Readout/store data only if discrepancy via VME

## **Conclusion**

• Trigger Primitive are generated using 2 boards:

- Front End board

- Trigger Concentrator Card

Both boards need test bench to validate the up-coming production

• Coherent test benches have been developed using same approach (XDAQ/HAL environment for VME, SystemC etc...) and even same hardware if possible

# Back-up slides

Latency: considering 2 c.u in FPGA + alignment  $\Rightarrow \leq 6$  clock unit (< requirement)