# Design and Realization of an ALICE SDD End-Ladder Prototype

Samuele Antinori - Davide Falchieri Alessandro Gabrielli - Enzo Gandolfi Massimo Masetti

I.N.F.N. Sezione di Bologna

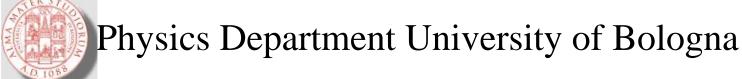

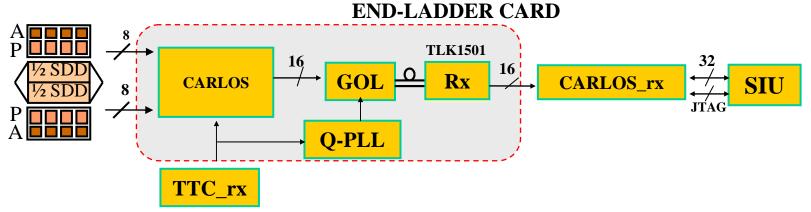

#### The Full ALICE SDD Readout Chain

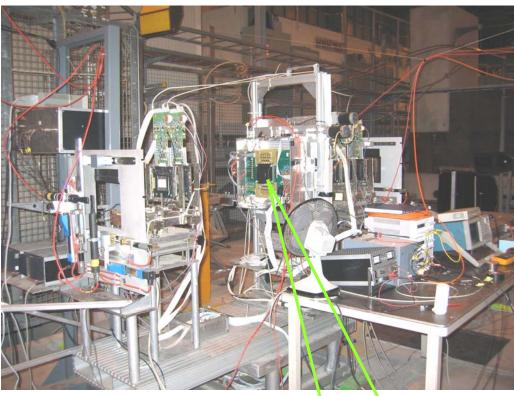

Test of the chain performed first in Bologna and then at CERN (2-3)

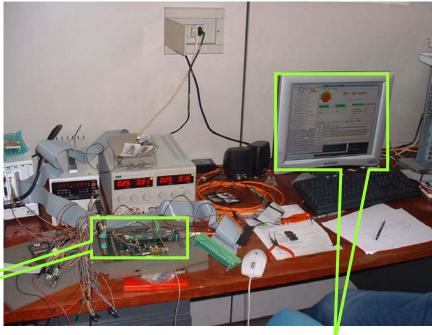

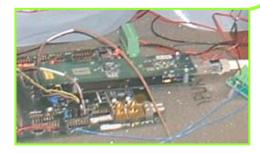

## The SDD Readout Chain in Bologna Lab

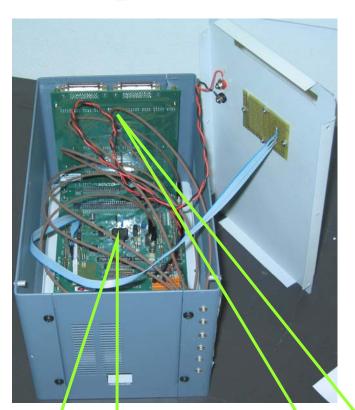

#### Implementation of the DDL card in Bologna (2004)

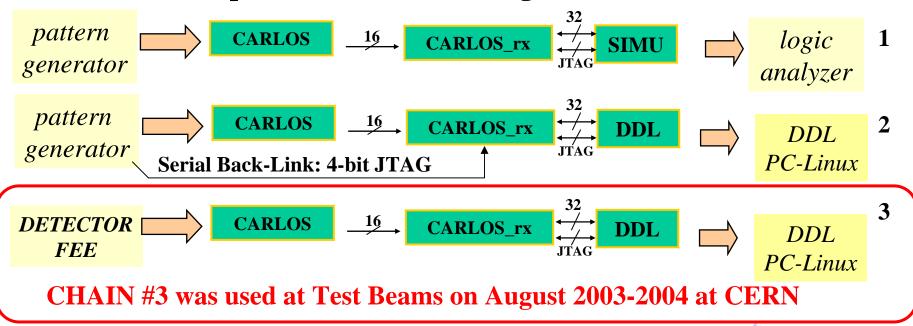

This is without Serializer-Deserializer and Optical Link between FEE and Carlos\_rx receiver card

Chain used for Test Beam 2004 at CERN

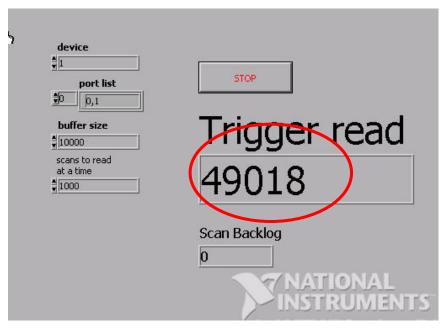

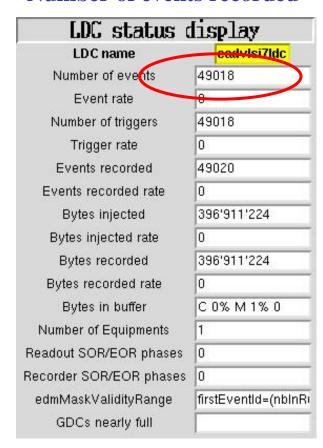

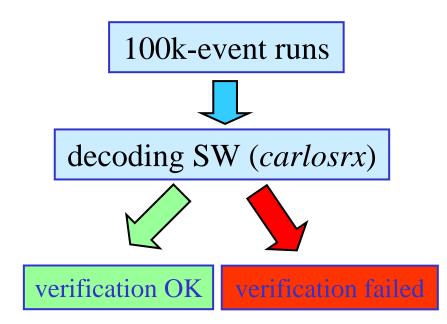

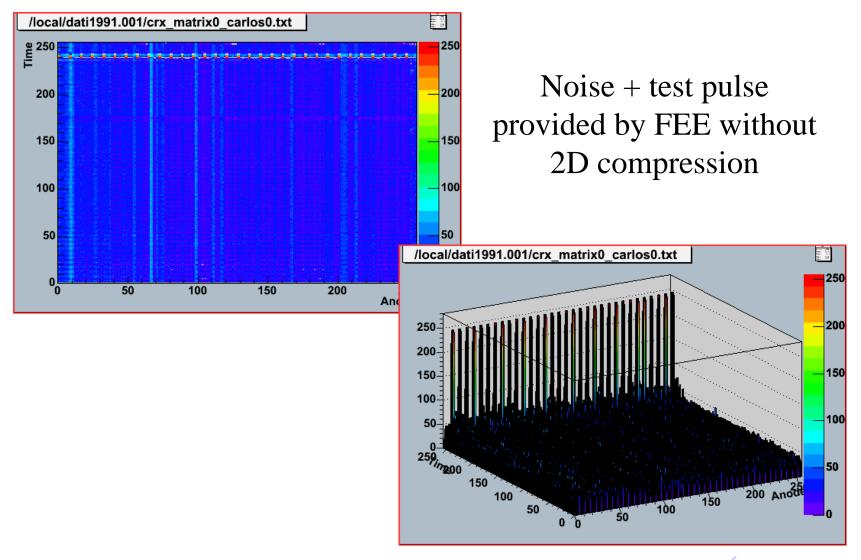

## DDL monitor when the chain is under test in Bologna Lab

#### **Number of triggers sent**

**PCI-6533 DIO-32HS**

#### **Number of events recorded**

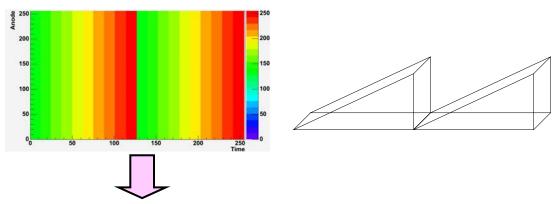

### Applying compression to the input pattern

saw-tooth shaped artificial dataset

#### DAQ readout chain with a given setup for 2D compression

2D compression enabled

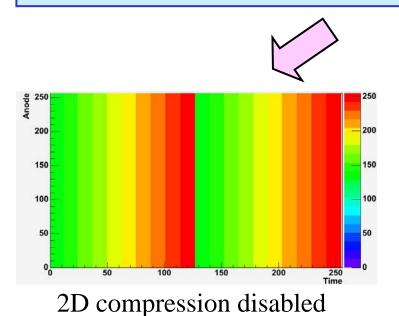

#### **Home-made Verification SW**

#### Test features:

- CARLOS programming via JTAG

- One Looped Event: 2.5k, 16k e 64k

- Back-pressure of CARLOSrx over CARLOS

- Trigger frequency (up to 550 Hz)

Upper limit (FEE) is 625 Hz

#### Tests with the FEE board

#### Implementation at Test-Beam on August 2004

Carlos\_rx card

Carlos card with prototype chip

SDD plus FEE with final chips

#### This is without Serializer-Deserializer and Optical Link

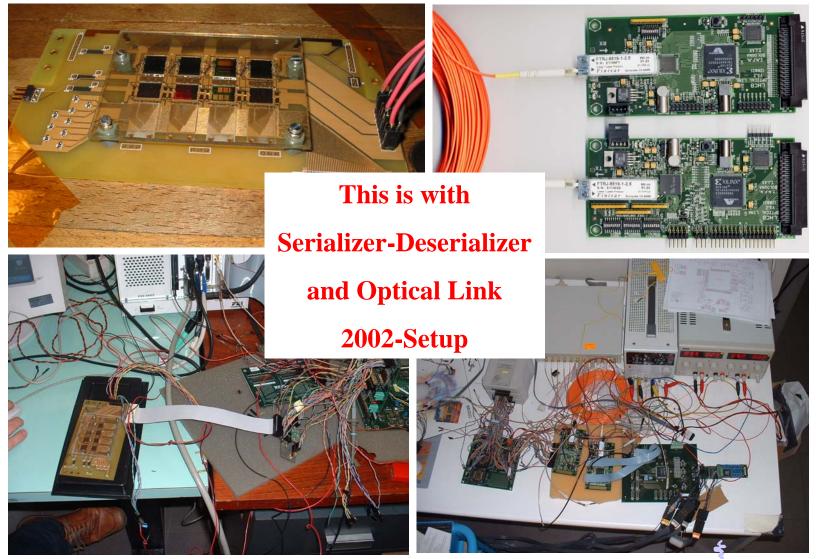

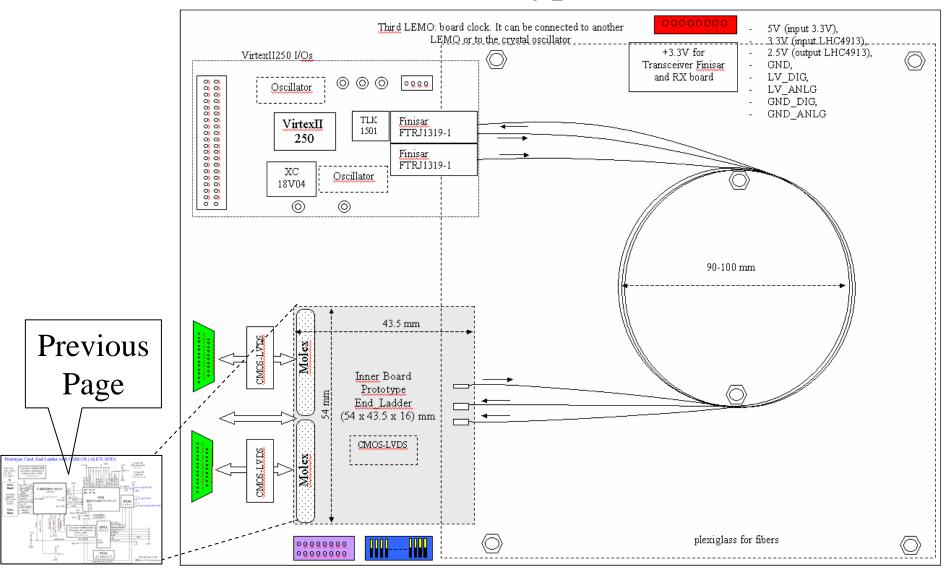

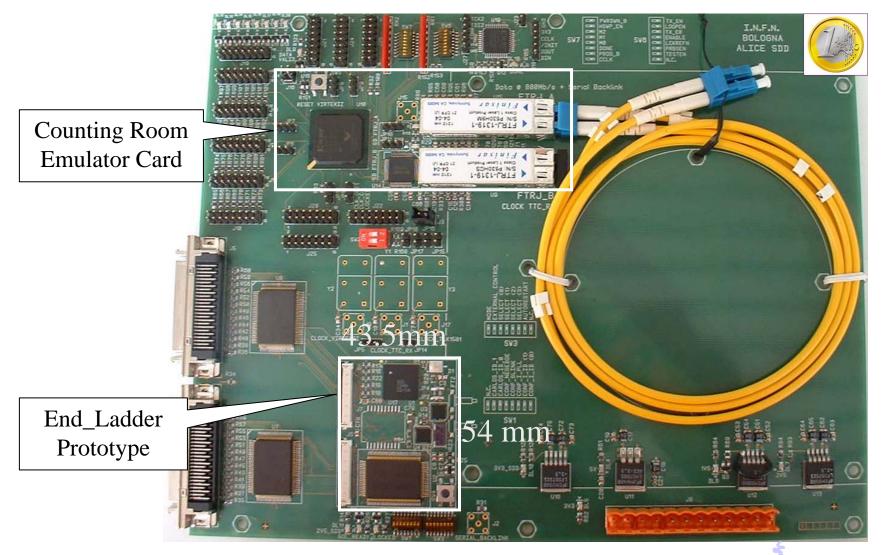

#### Prototype Card: End Ladder with CARLOS (ALICE SDD) 1310nm SM 2.5V ® 2.5V CMS photodiode ?x?x? GND DIG Convertitori CMOS-LVDS J<sub>SW×5</sub> GND ANLG da montare esternamente al 1310nm SM LV DIG prototipo di End Ladder CMS laser LV ANLG 17.2 x 23.2 x 2.5 4.5 x 4.0 x 1.35 conf\_neged( SCL selectDiff test\_shift i2c\_add(6-FF Flag(1:0) GND 2.5V GND data\_in0/1 (8:0) Molex ld\_cathode data out @ 800 Mb/s data write0/1 Bus0 CARLOSv4 (86 I/O) cav cav/tx er 22Ω data end0/1 〒100n COFP100 dav day / tx en Aft0/1 tx en all doubled 17.2 x 23.2 x 2.5 dis\_trigger Trigger0/1 signals for GOL ck @ 40 MHz din (15:0) Busy0/1 bus0/1 except reset gol reset b fpBGA (1mm) 13 x 13 x 1.6 RX40 JTAG 0/1 (4:0) ck\_out e JTAG GOL (4:0) clkLHC+ prepulse reset 0/1 5 x 5 x ? serial backlink @ 40 Mb/s gol ready ready data stop0/1 Molex ck out 180° prepulse phase shift jumper \\*< Bus1 Lvds40MHz+ test\_output (7:0) ck (CMOS) **......** 100Ω 🚺 Lvds40MHzserial back-link (CMOS) set\_test (2-0) carlos\_id (0-1) inLVDS+ inLVDS-1100 Ω **QPLL** external control Convertitore CMOS-LVDS foSelect (3:0) da montare sotto al prototipo $5 \times 5 \times ?$ di End Ladder inCMOS 2.5V N.C. 17.2 x 23.2 x 2.5 mode GND 100n сар 100 Ω ₩□◀ startup reset reset autorestart locked Strip -GND 2.5V 2.5V **XTAL** SW x 2 $3.7 \times 8.0 \times 1.75$ Pull-Up/Down 4.7 kΩ GND 100Ω on LVDS receiver pins serial back-link (LVDS)

## End-Ladder Prototype Sketch

## End-Ladder Prototype Picture

#### Work Plan

5/04: New and last CARLOS prototype submitted on MPW13

as half-production

9-10/04: Test of last CARLOS prototype on 20 packaged samples

10/04: Second part of the production on MPW14

10-12/04: Test of the complete DAQ chain from FEE to DDL

(prototype of the end-ladder board)

12/04-01/05: Packaging of the CARLOS production on BGA

1st\_Q/05: Test of the production (600 BGA packaged chips)

Possible design of a more accurate and-ladder card

End-Talk