# LECC 2004, Boston USA

# The Fast Merging Module (FMM) for readout status processing in CMS DAQ

Second and final prototype

attila.racz@cern.ch

on behalf of the CMS DAQ group

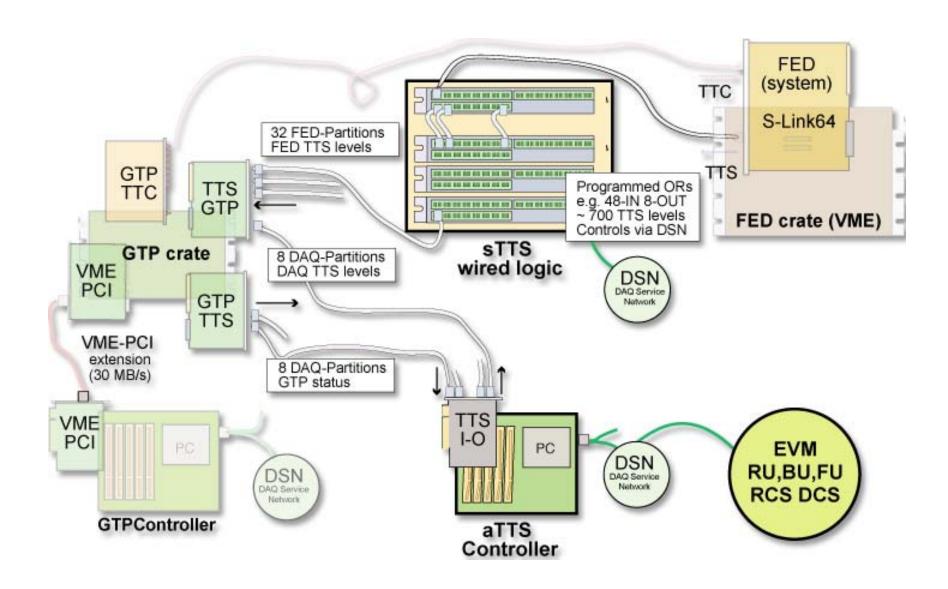

# **Trigger Throttling System**

- DAQ designed for 100 kHz maximum average trigger rate but...

- Higher instantaneous trigger rate is possible (Poisson)

- DAQ must not die by overflow if it happens! (and it will...)

- The TTS adapts the trigger pace with the DAQ processing capabilities

- sTTS for small buffer devices (fast response time, hardware parts)

- aTTS for large buffer devices (slow response time, software messages)

LECC 2004, Boston Attila RACZ / PH-CMD

# TTS global view

### **FMM** and sTTS

The FMM receives the current state of n devices and process them to form a single state that can be used by the TTS to modify (or not) the trigger rate

LECC 2004, Boston Attila RACZ / PH-CMD 4

## **FMM** design requirements

- Process (merges) the partition device states to form the detector partition status in a fast way (~100 ns)

- Monitors the dead time introduced by the partition devices

- Identification of (potential) pathologic FEDs

- Keeps a history memory of the state changes

- Allows to monitor the device states or playback for detailed analysis

- Generates input patterns for Trigger Control System

- Is also the output card for the aTTS

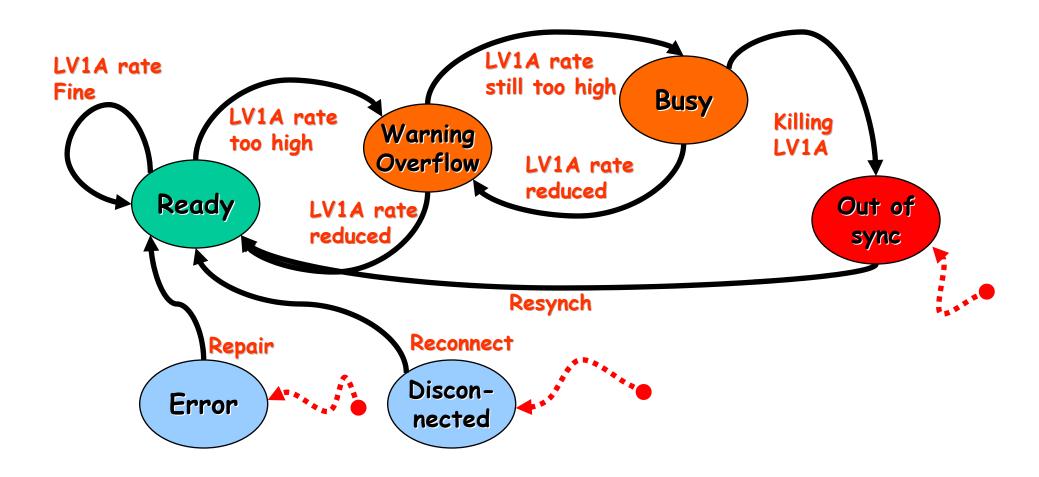

#### Partition device state machine

## State encoding and priorities

- States are provided on 4 bits: max transition rate = 40 MHz but we expect

~100 Hz!

- 6 states defined for FEDs using 7 values

- 9 values "reserved"

- If a FED is in any reserved state, the FMM propagates a new state: illegal

- FEDs linked to an FMM can be in a different state: state priorities (decreasing order) are as follows:

- Disconnect

- Error

- Out\_of\_sync

- Busy

- Overflow

- Illegal

- Ready

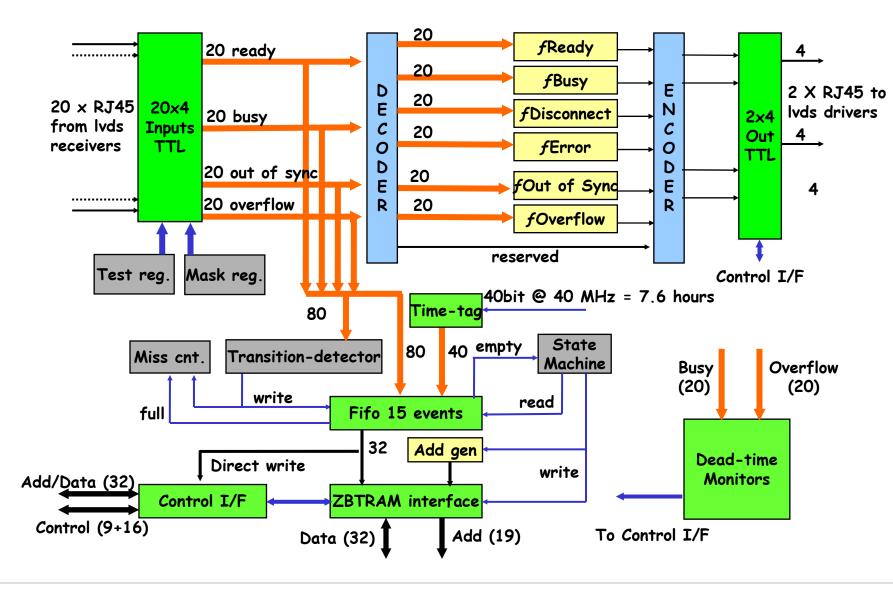

### **FMM features**

- 24 connectors with LEDs, configurable as input or output at soldering time

- Allows to deal with 1 or 2 partitions and enable the card to be aTTS output

- Mask register

- a pathologic FED will not disturb the system once detected and identified

- Hardware dead-time monitors

- early detection of potential problem

- Cyclic history memory: only state transitions are recorded with time tag

- 2 MB/128 k transitions (16 bytes/transitions)

- Time tag resolution/range: 25 ns/40 bit (~7.6 hours)

- System clock at 80 MHz, Inputs sampled at 80 MHz but processed at 40 MHz

- History data can be pushed directly to host PC ("ala" FEDKIT)

- FPGA configuration files can be updated from PCI and on-board JTAG

# **Processing/Merging functions**

- Depending on the states

- Logical OR

- Arithmetic sum & threshold

- Can be modified on request thanks to the on-board FPGA

### **FMMs in CMS**

- FMM with 20 inputs max, 4 outputs: modulable in 20->1, 2x [10->1] (½)

- Double outputs are needed on the last FMM in the tree

- In this case, 8 FMMs per crate, one slot for reset distribution, 6 crates total

| Detector<br>(# of FEDs) | Partition<br>(# of FEDs) | # of FMM per<br>partition | # of FMM per<br>detector |

|-------------------------|--------------------------|---------------------------|--------------------------|

| Pixel                   | Barrel (32)              | 2+ 1/2                    | 3                        |

| (38)                    | Forward (6)              | 1/2                       |                          |

|                         | Inner (114)              | 6+ 1/2                    | 25                       |

| Tracker                 | Outer (134)              | 7+ 1/2                    |                          |

| (440)                   | Endcap+(96)              | 5+ ½                      |                          |

|                         | Endcap-(96)              | 5+ 1/2                    |                          |

| Preshower               | SE+ (25)                 | <b>2+</b> ½               | 5                        |

| (~50)                   | SE- (25)                 | <b>2+</b> ½               |                          |

|                         | EB+ (18)                 | 1                         | 3                        |

| ECAL                    | EB- (18)                 | 1                         |                          |

| (54)                    | EE+ (9)                  | 1/2                       |                          |

|                         | EE- (9)                  | 1/2                       |                          |

|                         | HB+ (6)                  | 1/2                       | 3                        |

| HCAL                    | HB- (6)                  | 1/2                       |                          |

| (32)                    | HE+ (5)                  | 1/2                       |                          |

|                         | HE- (5)                  | 1/2                       |                          |

|                         | HO+ (5)                  | 1/2                       |                          |

|                         | HO- (5)                  | 1/2                       |                          |

| Detector<br>(# of FEDs)           | Partition<br>(# of FEDs)                 | # of FMM per<br>partition          | # of FMM per<br>detector |

|-----------------------------------|------------------------------------------|------------------------------------|--------------------------|

| Mu-DT<br>(5)                      | Barrel+<br>Barrel-                       | 1/ <sub>2</sub> 1/ <sub>2</sub>    | 1                        |

| Mu-RPC<br>(6)                     | Barrel+<br>Barrel-<br>Endcap+<br>Endcap- | ½<br>½<br>½<br>½<br>½              | 2                        |

| Mu-CSC<br>(8)                     | Endcap+<br>Endcap-                       | 1/ <sub>2</sub><br>1/ <sub>2</sub> | 1                        |

| Calo-trig<br>Glob–mu<br>Glob-trig | Na<br>Na<br>Na                           | 1/2<br>1/2<br>1/2                  | 2                        |

| Mu-trig                           | CSC-trig<br>DT trig                      | 1/ <sub>2</sub> 1/ <sub>2</sub>    | 1                        |

| Total                             | 31 (636)                                 |                                    | 46                       |

## **History capacity and BW**

- Each transition generates 80 bits (4 x 20) + 40 bits (time tag) or 16 bytes

- 1MB of memory is 64K transitions

- Worst case bandwidth on PCI backplane is 12MB/sec (with 8 FMMs per crate)

- External memory of 2 MB is chosen

| Transition rate (all inputs) | History<br>length per<br>MB (second) | Data rate to<br>the history<br>memory |

|------------------------------|--------------------------------------|---------------------------------------|

| 10Hz                         | 65000<br>(1.8 hour)                  | 160 bytes/sec                         |

| 100Hz                        | 655<br>(~11 min)                     | 1.5 kB/sec                            |

| 1kHz<br>Worries              | 65                                   | 15 kB/sec                             |

| 10kHz<br>Pathologic          | 6.5                                  | 156 kB/sec                            |

| 100kHz<br>Very<br>Pathologic | 0.65                                 | 1.5 MB/sec                            |

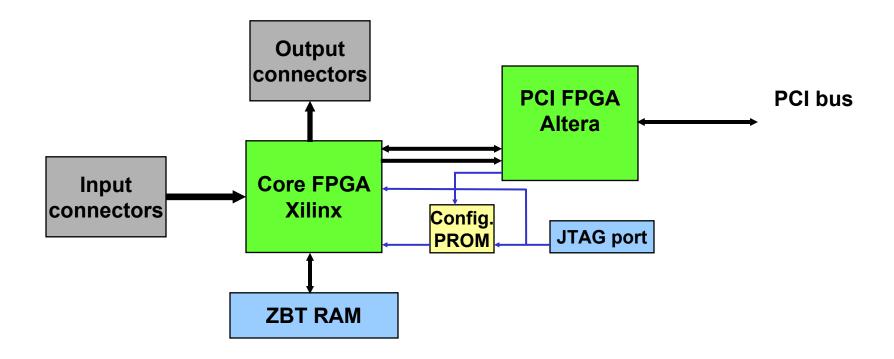

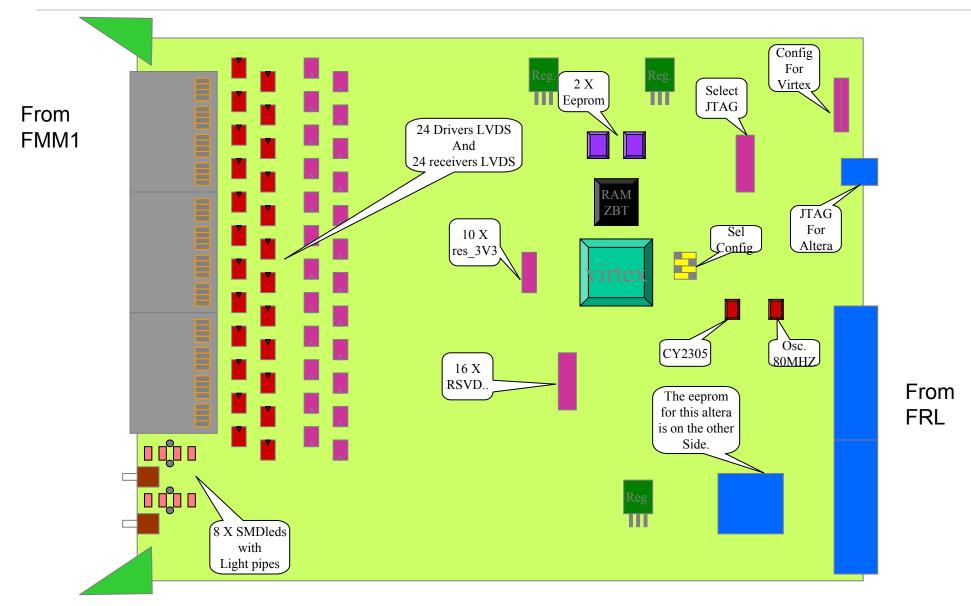

# **Block diagram**

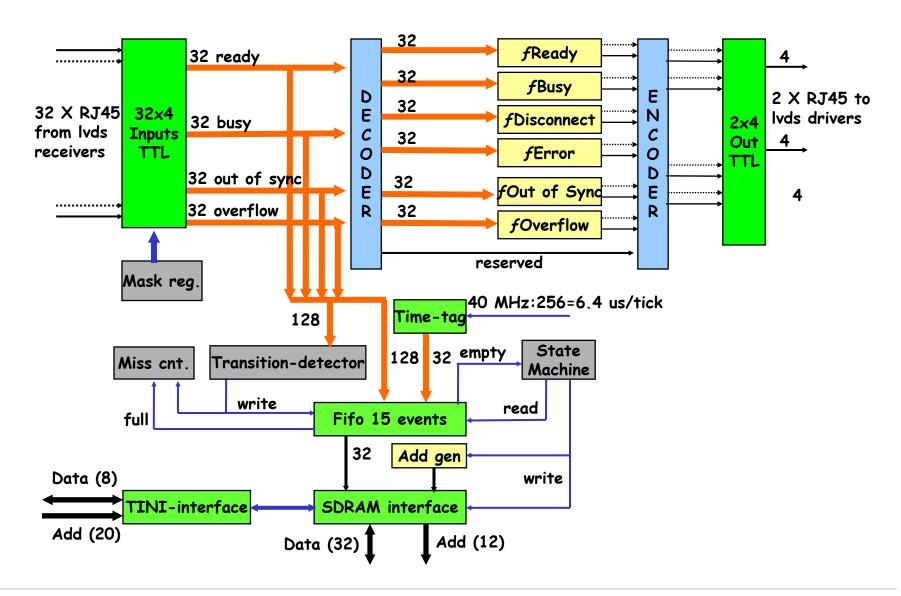

# FPGA block diagram (20 inputs)

## **FMM** implementation

- Compact PCI 6U double width form factor

- TTS connector allows standard RJ45 network cables

- At 40 MHz transition rate, LVDS drivers allows hundreds meter of cable length

- PCI control interface re-used from FRL design

- Same location of JTAG port

- enables the re-use of FRL testbed

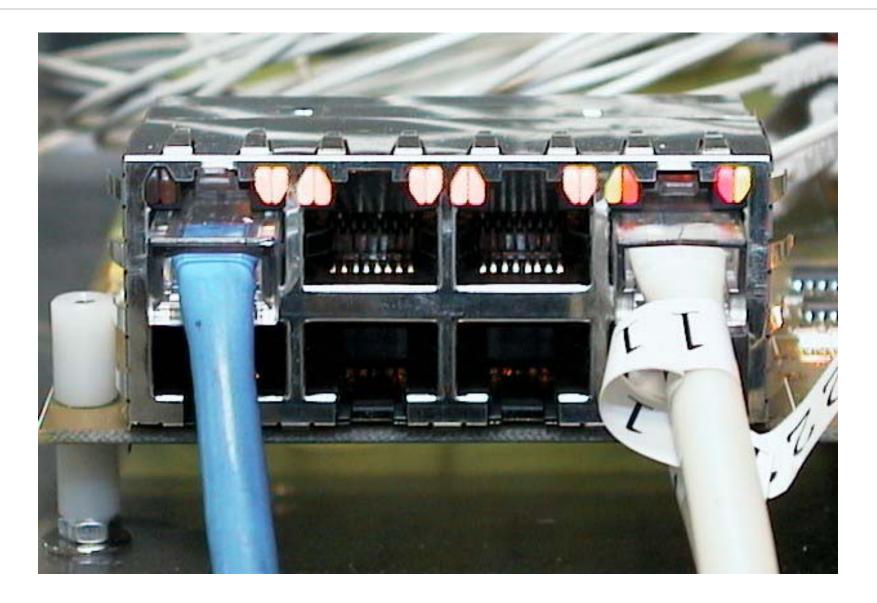

#### **TTS** connector

- Standard RJ45 connector is used

- Low cost, reliable, small footprint, high-density front panel

Socket with light-guides for bi-color LEDs

- Pin 1 -busy

- Pin 2 +busy

- Pin 3 -ready

- Pin 4 +overflow warning

- Pin 5 -overflow warning

- Pin 6 + ready

- Pin 7 -out of synch

- Pin 8 +out of synch

# I/O block

### **Core FPGA**

- I/O count: ~224 pins

- 24 TTS inputs/outputs: 96 pins

- Control I/F (32 A/D+misc): 48 pins

- − Memory I/F (32D/20A): ~60 pins

- Misc. (Leds, prom, reset...) ~20 pins

- Logic gates: ~ 5000 FF (estimates based on proto1)

- Memory I/F: 300FF, 100 LUT

- Logic: ~750FF, ~875 LUT

- Monitors (raw counters): 3200FF, (4 states monitored)

- Pattern injection logic: ~700FF (comfortable...)

- Xilinx XC2VP7-5FG456 is selected: 248 I/Os, 10000 FF

LECC 2004, Boston Attila RACZ / PH-CMD

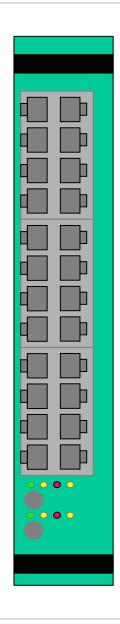

#### **Front Panel**

- 2U wide, 6U height Compact PCI

- Same format as FRL

- 24 TTS I/O

- 8 status leds

- 2 push-buttons: reset and reprog Core FPGA

# **PCB** layout

# **Prototype picture**

# CMS

#### **Status**

- 2 PCB produced and populated

- Register/memory tests passed

- Inputs/Outputs tested "one by one" at computer speed

- Wait after a "helper module" to stress all inputs at 40 MHz

- After... we enter production!

- Production test software being debugged

# End

## What next after first prototype...

- Design the final prototype with

- PCI interface

- Compact PCI form factor (6 or 9U)

- See if 32 inputs is optimal

- Implement hardware monitoring engines

LECC 2004, Boston Attila RACZ / PH-CMD 23

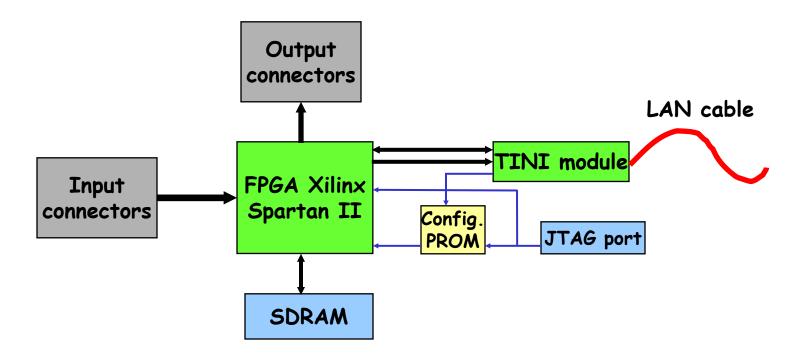

## First prototype

- Validation of FMM concept

- 19-inch rack mounted 1U box

- A Xilinx Spartan II is the core FPGA

- Standard UTP5 Input connector running LVDS levels

- External SDRAM for history memory

- TINI module (WEB) used as control interface

- No deadtime monitor engine

- Core FPGA functions validated

# First proto block diagram

# First proto FPGA block diagram

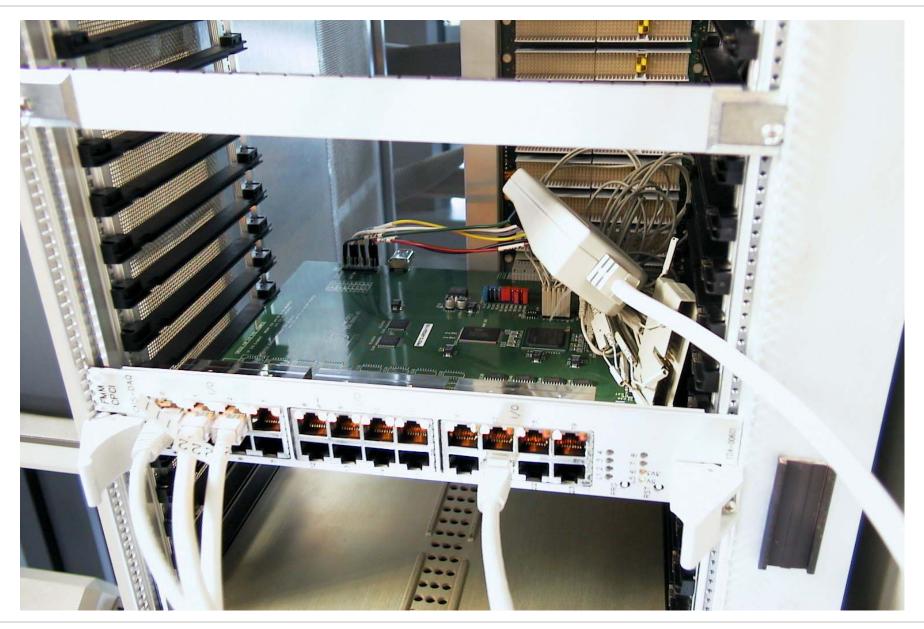

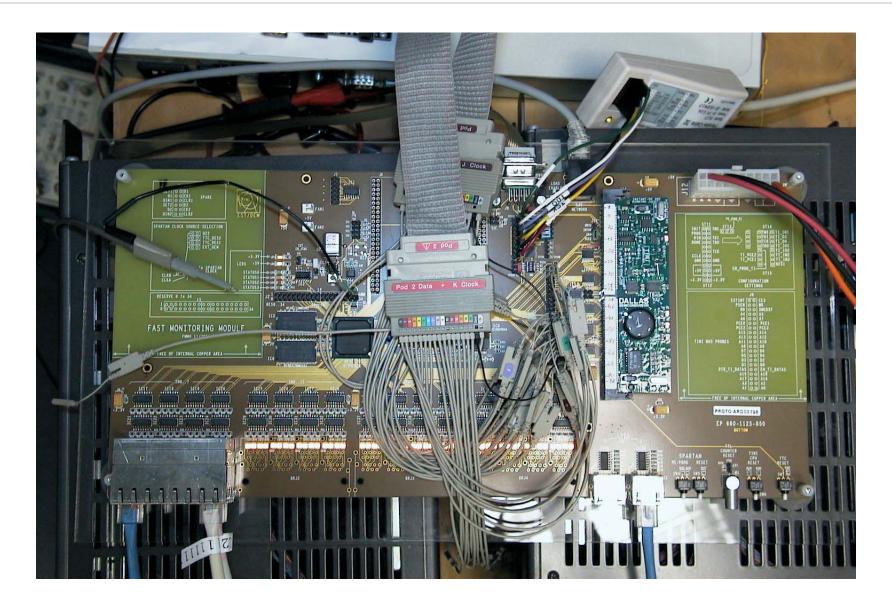

# First prototype picture

## First prototype performances

- History memory

- 16 MB/840 k transitions (20 bytes/transitions)

- Time tag resolution/range: 6.4 us/32 bit (~7.6 hours)

Propagation time: 100 ns (4 clock cycles @ 25 ns)

LECC 2004, Boston Attila RACZ / PH-CMD 28