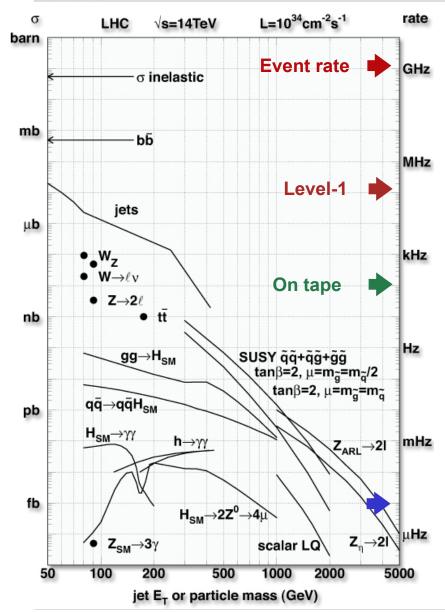

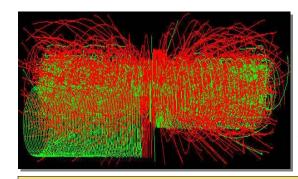

### p-p collisions at LHC

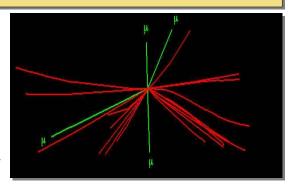

Operating conditions: Higgs in 4 muons + ~20 minimum bias

All charged tracks with pt > 2 GeV

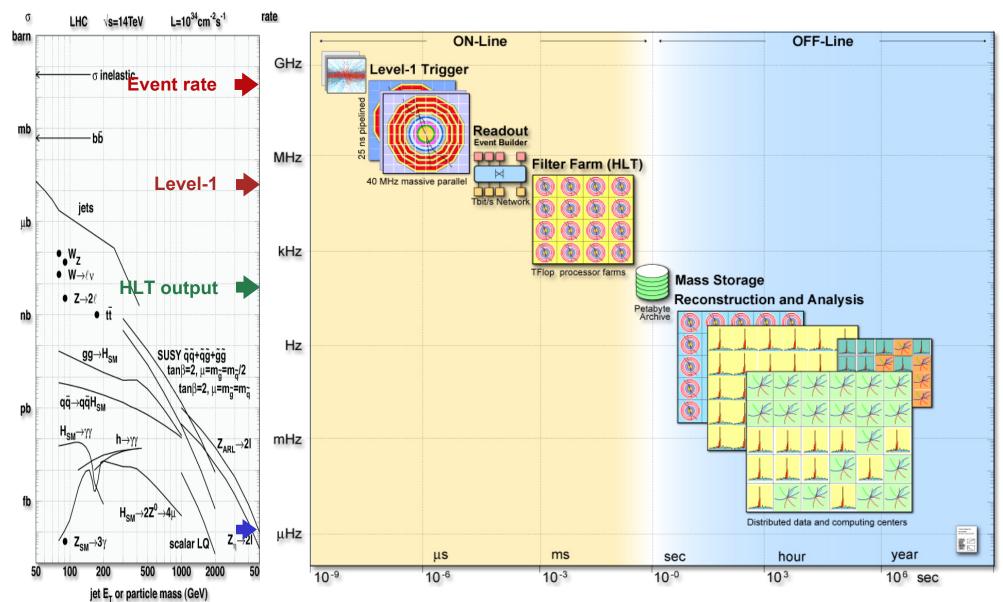

Event Rates: ~109 Hz

**Event size:**

~1 MByte

Level-1 Output

Mass storage

Event Selection:

100 kHz 10<sup>2</sup> Hz ~1/10<sup>13</sup>

Reconstructed tracks with pt > 25 GeV

### Requirements and design parameters

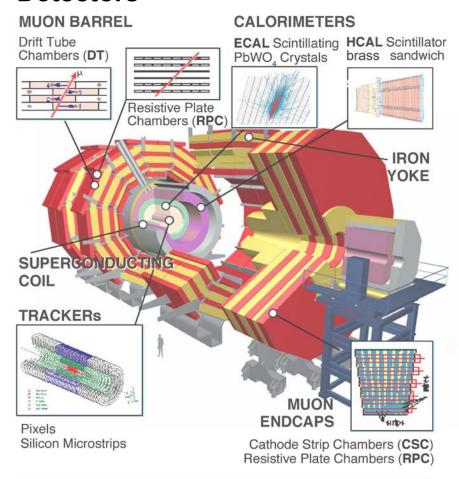

#### **Detectors**

Total weight: 12,500 t Overall length: 21.6 m

Overall diameter: 15 m Magnetic field: 4 Tesla

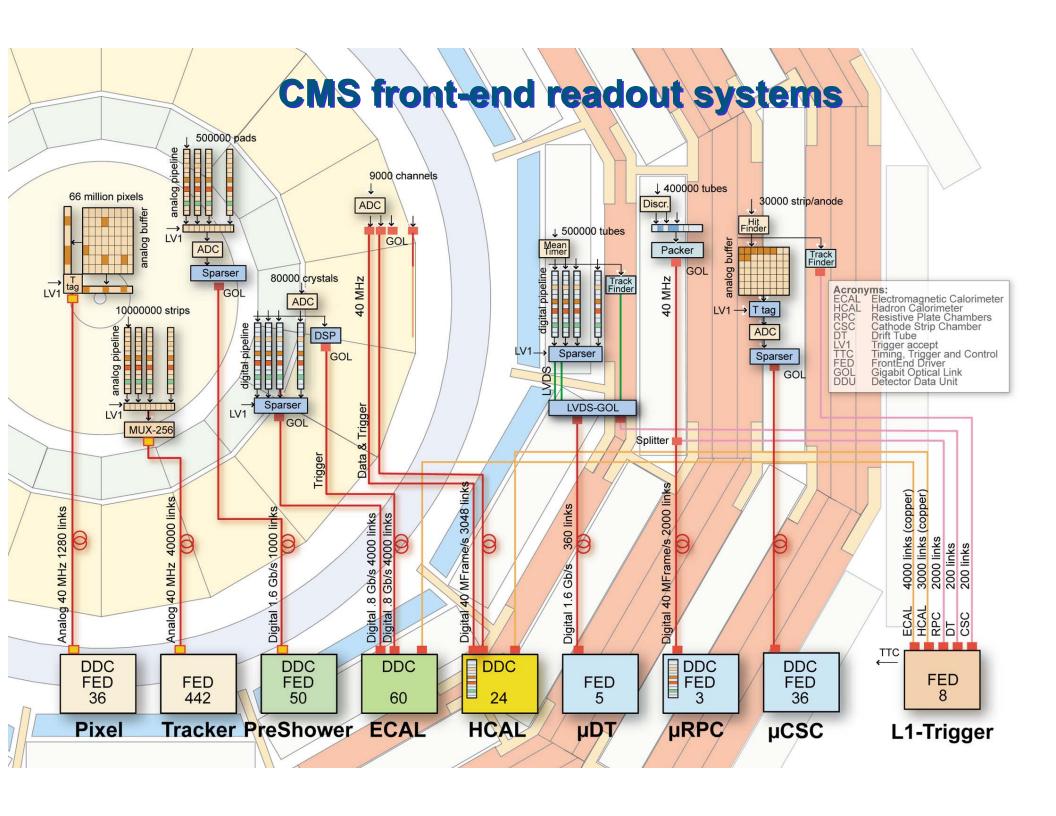

#### **Detector Channels Control Ev. Data**

| Pixel     | 60000000 | 1 GB   | 50 (kB)    |

|-----------|----------|--------|------------|

| Tracker   | 10000000 | 1 GB   | 650        |

| Preshower | 145000   | 10 MB  | <b>5</b> 0 |

| ECAL      | 85000    | 10 MB  | 100        |

| HCAL      | 14000    | 100 kB | <b>5</b> 0 |

| Muon DT   | 200000   | 10 MB  | 10         |

| Muon RPC  | 200000   | 10 MB  | 5          |

| Muon CSC  | 400000   | 10 MB  | 90         |

| Trigger   |          | 1 GB   | 16         |

|           |          |        |            |

Event size

Max LV1 Trigger

Online rejection

System dead time

1 Mbyte 100 kHz 99.999%

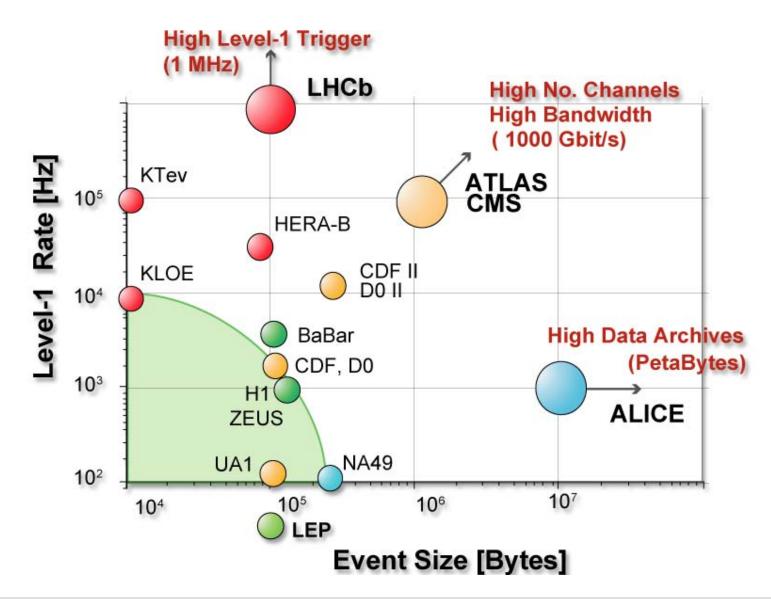

## LHC trigger and DAQ summary

| ATLAS                               | <b>No.Levels</b><br>Trigger | First Level<br>Rate (Hz)             | <b>Event</b><br>Size (Byte)         | <b>Readout</b> Bandw.(GB/s) | Archive<br>MB/s (Event/s)                                       |

|-------------------------------------|-----------------------------|--------------------------------------|-------------------------------------|-----------------------------|-----------------------------------------------------------------|

| CMS                                 | <b>3</b>                    | 10 <sup>5</sup><br>210 <sup>3</sup>  | <b>10</b> <sup>6</sup>              | 10                          | <b>100</b> (10 <sup>2</sup> )                                   |

|                                     | 2                           | 10 <sup>5</sup>                      | <b>10</b> <sup>6</sup>              | 100                         | <b>100</b> (10 <sup>2</sup> )                                   |

| LHCb                                |                             | 10 <sup>6</sup><br>4 10 <sup>4</sup> | 2×10 <sup>5</sup>                   | 4                           | <b>40</b> (2x10 <sup>2</sup> )                                  |

| PHOS TIC ASSOSEE MECHEPIUM MICHIBEL | -                           | 500<br>10 <sup>3</sup>               | 5x10 <sup>7</sup> 2x10 <sup>6</sup> | 5                           | <b>1250</b> (10 <sup>2</sup> )<br><b>200</b> (10 <sup>2</sup> ) |

### Trigger and data acquisition trends

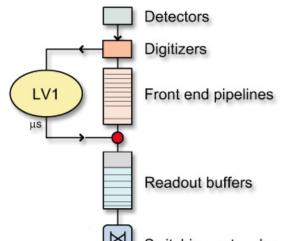

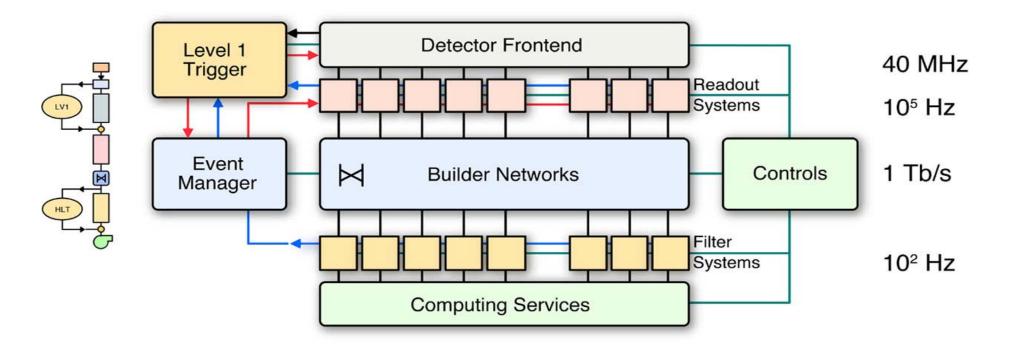

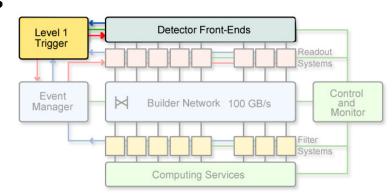

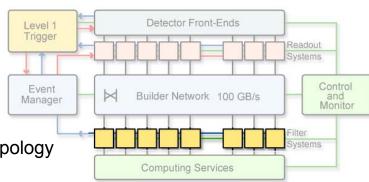

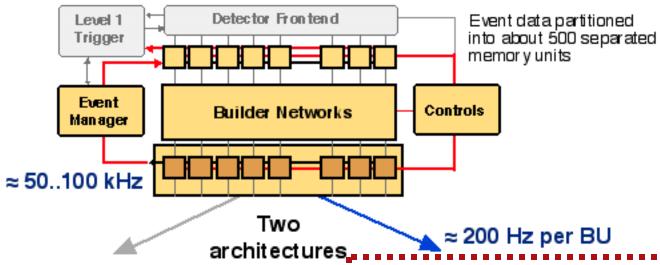

### CMS DAQ structure: 2 physical triggers

40 MHz

**Clock driven Custom processors**

Level-1 Trigger Custom design

100 kHz Event driven PC network

High-Level Trigger Industry products

Level-1 output / HLT input 100 kHz

Network bandwidth 1 Terabit/s

HLT output 10<sup>2</sup> Hz

Invest in data transportation and CPU

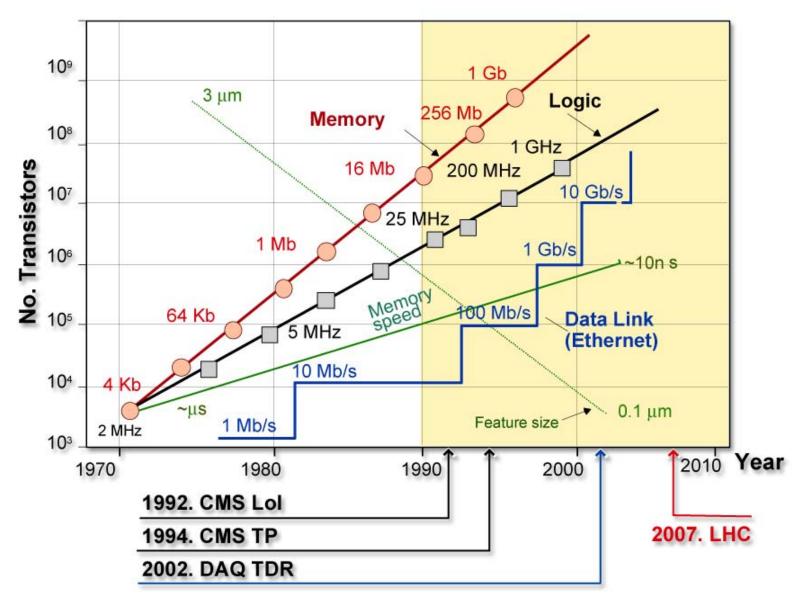

## Evolution of DAQ technologies and structures

#### 1970-80: Minicomputers

Readout custom design First standard: CAMAC

kByte/s

#### 1980-90: Microprocessors

HEP standards (Fastbus) Embedded CPU, Industry standards (VME)

MByte/s

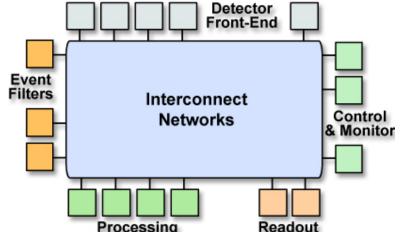

#### 2000-xx: Networks

IT commodities, PC, Clusters Internet, Web, etc.

GByte/s

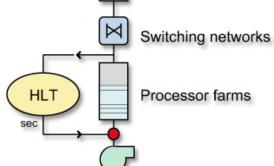

### **DAQ** baseline structure

Collision rate 40 MHz No. of In-Out units 512

Level-1 Maximum trigger rate 100 kHz Readout network bandwidth ≈ 1 Terabit/s

Average event size ≈ 1 Mbyte Event filter computing power ≈ 10<sup>6</sup> SI95

Event Flow Control ≈ 10<sup>6</sup> Mssg/s Data production ≈ Tbyte/day

No. of PC motherboards ≈ Thousands

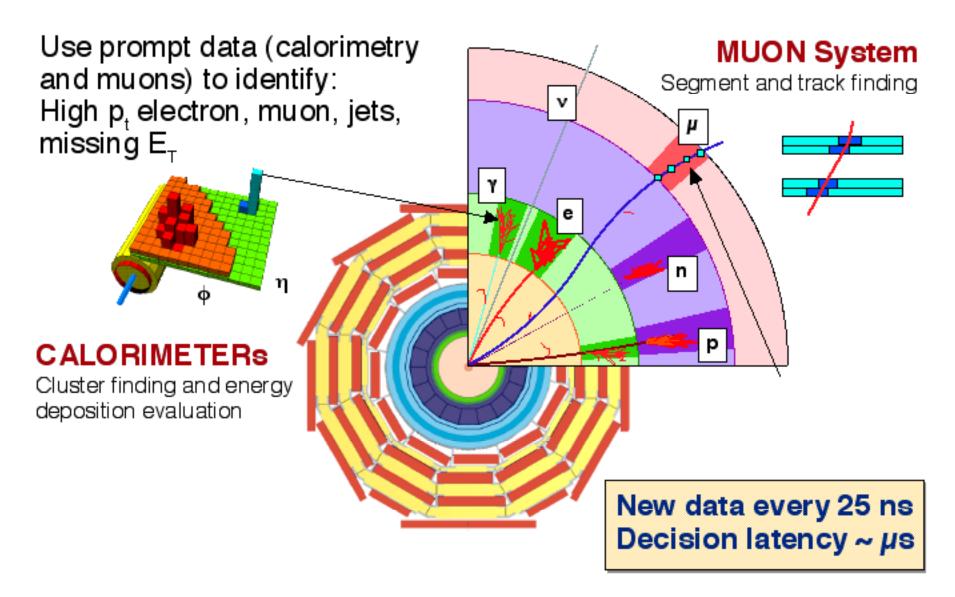

### Two trigger levels

## Level-1: Specialized processors 40 MHz synchronous

- -Particle identification:

- -high pT electron, muon, jets, missing ET

- Local pattern recognition and energy evaluation on prompt macro-granular information from calorimeter and muon detectors

### 99.99 % rejected 0.01 Accepted

## High trigger levels: CPU farms 100 kHz asynchronous farms

- Clean particle signature

- Finer granularity precise measurement

- Kinematics. effective mass cuts and event topology

- Track reconstruction and detector matching

- Event reconstruction and analysis

100-1000 Hz. Mass storage Reconstruction and analysis.

99.9 % rejected 0.1 Accepted

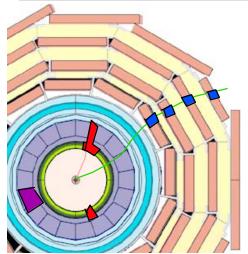

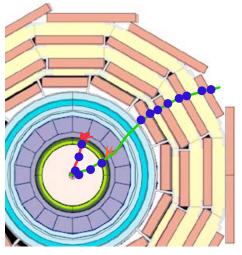

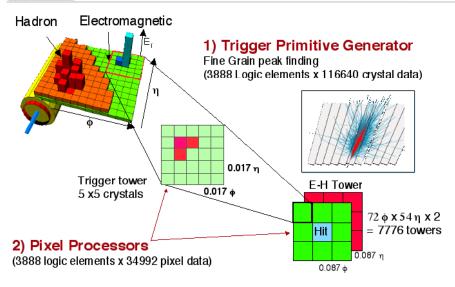

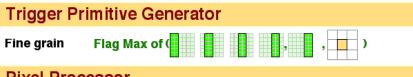

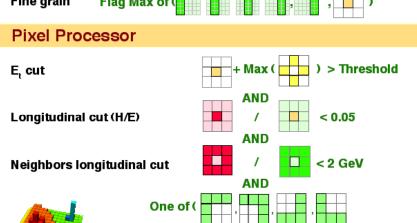

### Level-1. Particle identification

### **Level-1 trigger systems**

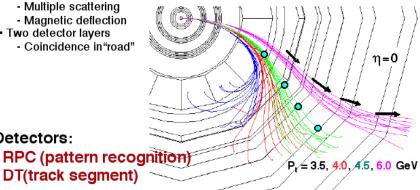

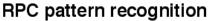

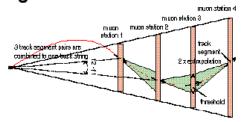

#### Trigger based on tracks in external muon detectors that point to interaction region

- Low-p<sub>↑</sub> muon tracks don't point to vertex

- Multiple scattering

- Magnetic deflection

- Two detector layers

- Coincidence in "road"

ISOLATED ELECTRON

- Pattern catalog

- Fast logic

Detectors:

#### DT and CSC track finding:

- Finds hit/segments

- Combines vectors

- Formats a track

- Assigns p. value

### **High Level Trigger: Event Filter farm**

Massive parallel system

ONE event, ALL processors

- Low latency

- Complex I/O

- Parallel programming

## Farm of processors ONE event, ONE processor

- High latency (larger buffers)

- Simpler I/O

- Sequential programming

### **Technology trends**

### Readout and computing IO structures

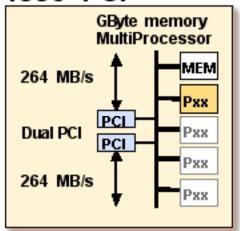

#### 1990' PCI

IO and Processing systems : Commercial PCs

Operating systems : Unix(Linux),

Interfaces standards : PC IO systems (e.g. PCI)

Desktop/Server current architecture Peripheral IO bus PCI: 33/66 MHz x 32/64 bit 100/200/400 MB/s

200X: PCI-X ...

#### 2002 PC mother boards:

- 2 GHz dual processors

- 4 PCI-X ports at 1GB/s

- 3 GB/s memory bandwidth

- Suitable for all DAQ readout applications

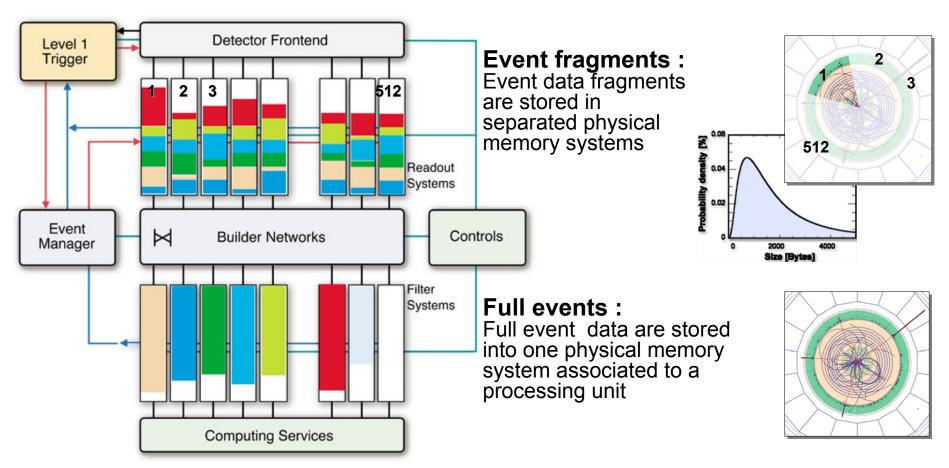

### **Building the event (EVB)**

#### **Event builder:**

Physical system interconnecting data sources with data destinations. It has to move each event data fragments into a same destination

## 512 Data sources for 1 Mbyte events ~1000s HTL processing nodes

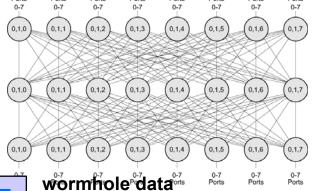

### **EVB** and switch technologies

### **Myricom Myrinet 2000**

• NIC: M3S-PCI64B-2 (LANai9)

Custom Firmware

#### Implementation:

16x16 port X-bar capable of channeling data between any two ports.

transport with flow control at all stages

### **Gigabit Ethernet**

• Switch: Foundry FastIron 64 x 1.2 Gb/s port

NIC: Alteon (running standard firmware)

#### Implementation:

Multi-port memory system of R/W access bandwidth greater than the sum of all port speeds

Packet switching

Contention resolved by Output buffer. Packets can be lost.

Infiniband • 2.5 Gb/s demo product. Tests ongoing with a small 2x2 setup

150

100

50

0

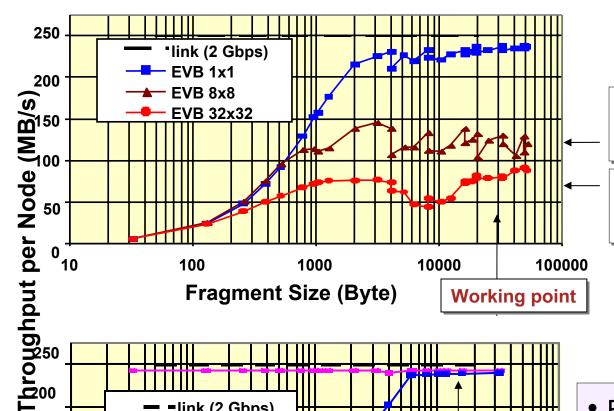

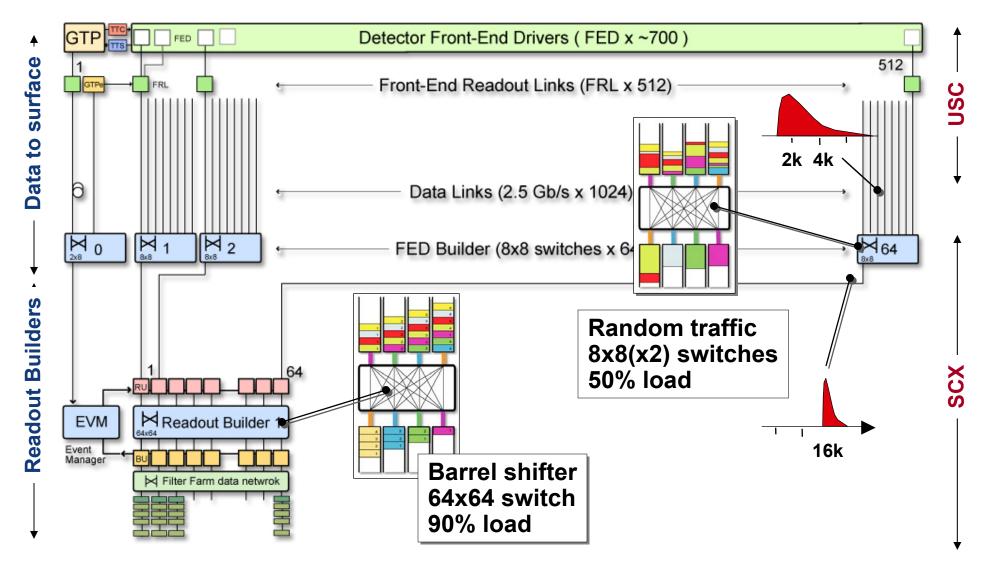

### 32x32 Myrinet EVB protocols results

#### Random traffic

**8x8:** single stage:

max. utilization: ≈ 50%

**32x32**: two stage network

max. utilization  $\approx 30\%$

### **Barrel shifter**

- Fixed size event fragments below 4k: Fragment < BS carrier above 4k: Fragment > BS carrier

- Throughput at 234 MB/s = 94% of link Bandwidth

-link (2 Gbps)

EVB - fixed size

BS@NIC

100000

10000

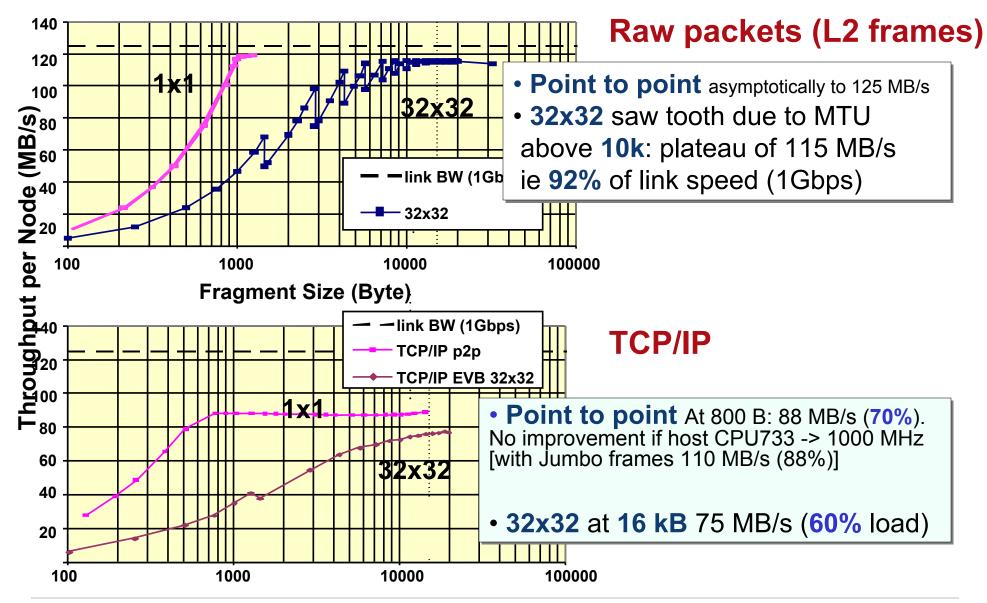

### 32x32 GbE EVB protocols results

### **EVB** demonstrators summary

|                | Myrinet 2000 | GbE raw packet            | GbE TCP/IP                |

|----------------|--------------|---------------------------|---------------------------|

| Test bench     | 32x32        | 32x32                     | 32x32                     |

| Port speed     | 2.5 Gbit/s   | 1.2 Gbit/s                | 1.2 Gbit/s                |

| Random traffic | 30-50%       | 50%, <mark>92%</mark> (*) | 30%, <mark>60%</mark> (*) |

| Barrel switch  | 94%          | -                         | -                         |

| CPU load       | Low          | High                      | High                      |

| 1 Tbit/s EVB   | 512x512      | 1024x1024                 | 2048x2048                 |

| No. switches   | 8 128-Clos   | 16 256-port               | 32 256-port               |

(\*) with fragment sizes larger than 16kB

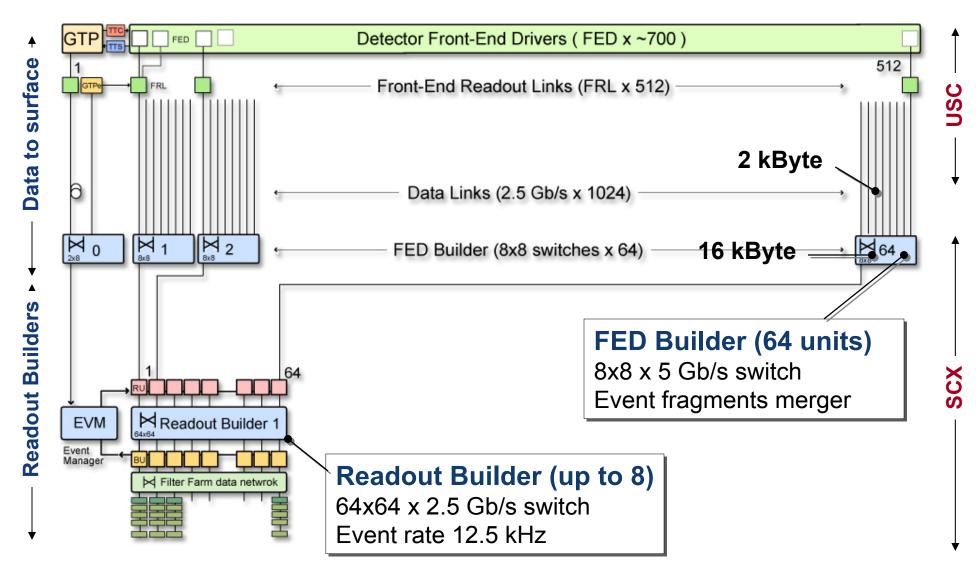

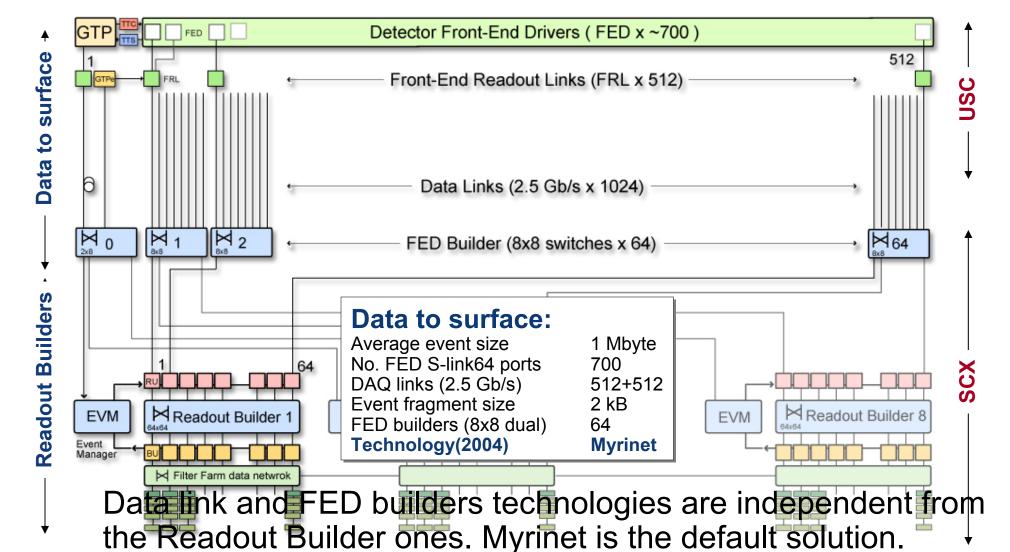

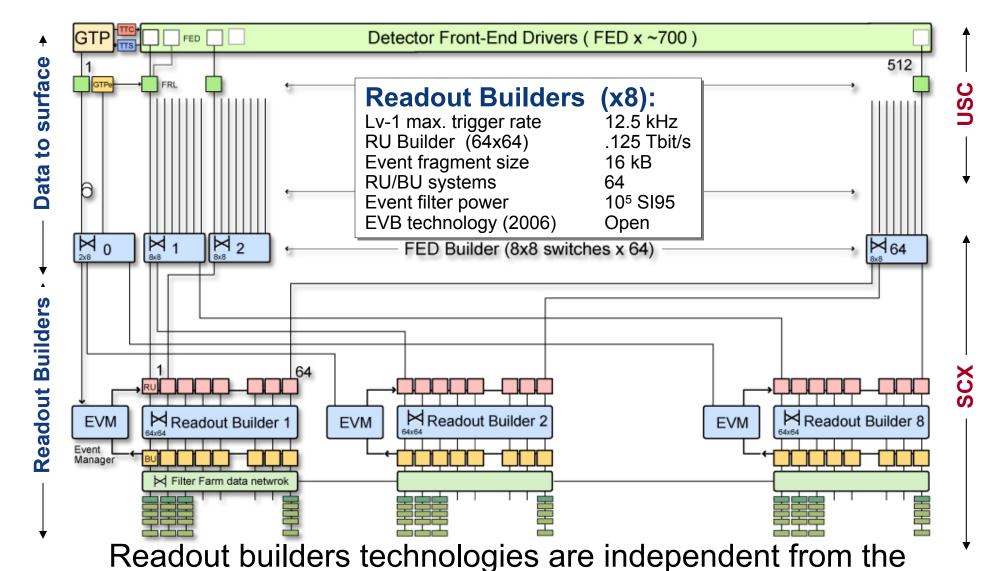

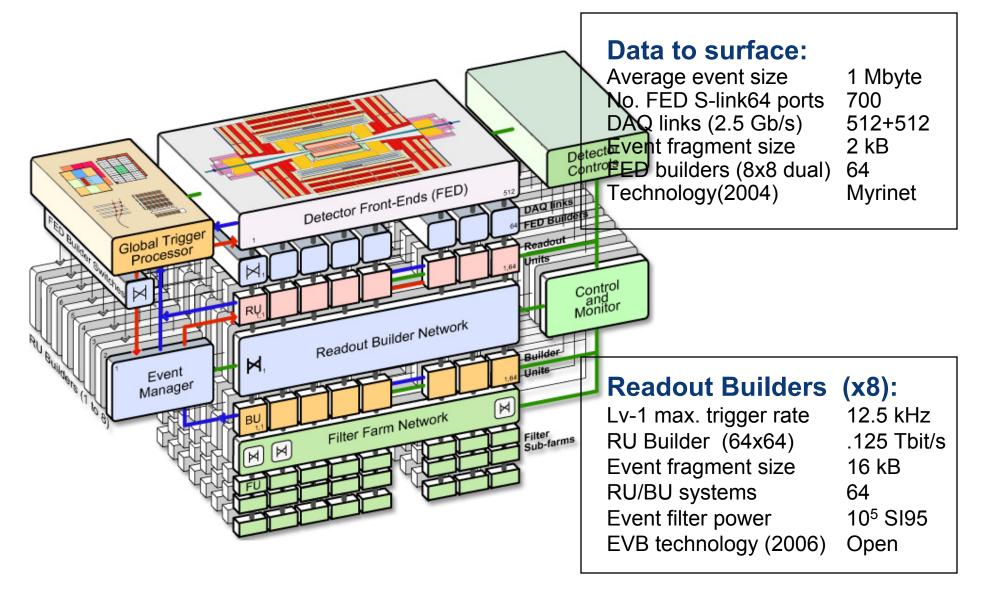

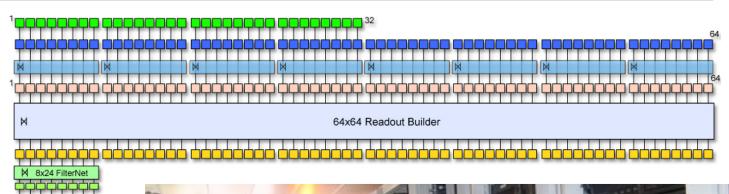

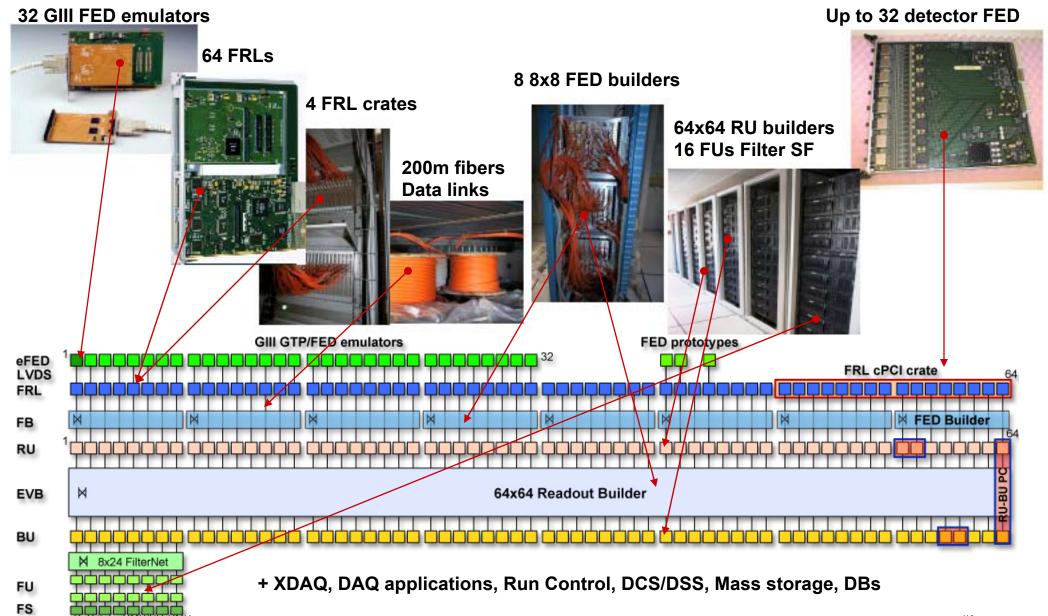

## 2 stages: Data to surface & Readout Builder

### **Builders protocols (e.g. Myrinet)**

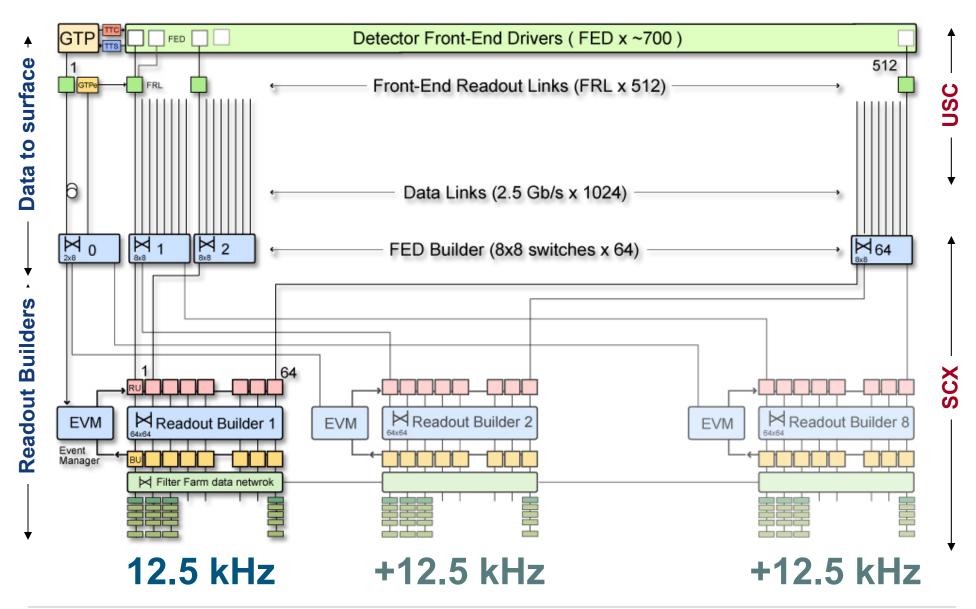

### DAQ staging: 1 to 8 RBs = 100 kHz

### I) Data to surface (D2S)

Decision must be taken in 2004. Installation in 2005

### II) Readout Builders (RB)

D2S one. Decision will be taken later in 2006

### 8-fold DAQ 3-D design

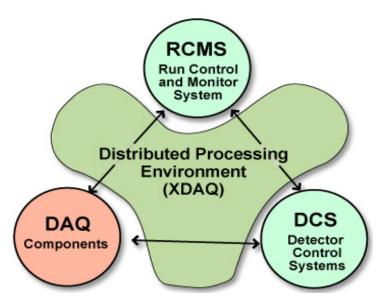

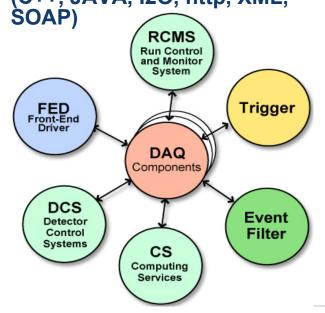

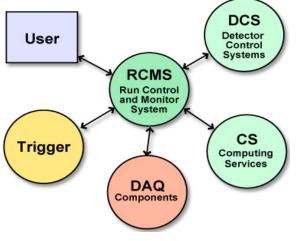

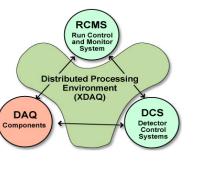

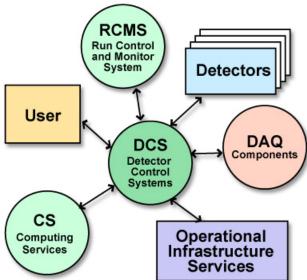

## On-line software: framework and subsystems

#### Online software architecture:

- Cross-platform DAQ framework: XDAQ

- Data acquisition components

- Run Control and Monitor System (RCMS)

- Detector Control System (DCS)

The RCMS, DCS and data acquisition components interoperate through a distributed processing environment called XDAQ (cross-platform DAQ framework)

S. Cittolin CMS/PH-CMD

### Configuration, operation and monitoring

## XDAQ:on-line framework and DAQ components:

• Services and tools for local and remote inter-process communication, configuration and control and data storage Components to build data acquisition systems (RU,BU,EVM,..) (C++, JAVA, I2O, http, XML,

# RCMS: Run Control and Monitoring System Based on open protocols, web

Based on open protocols, web services and emerging e-tools tools (JAVA, http, XML, MySQL, ....)

#### **DCS: Detector Control Systems**

Based on industry supported hardware and software (PLC, field buses, PVSS and JCOP tools)

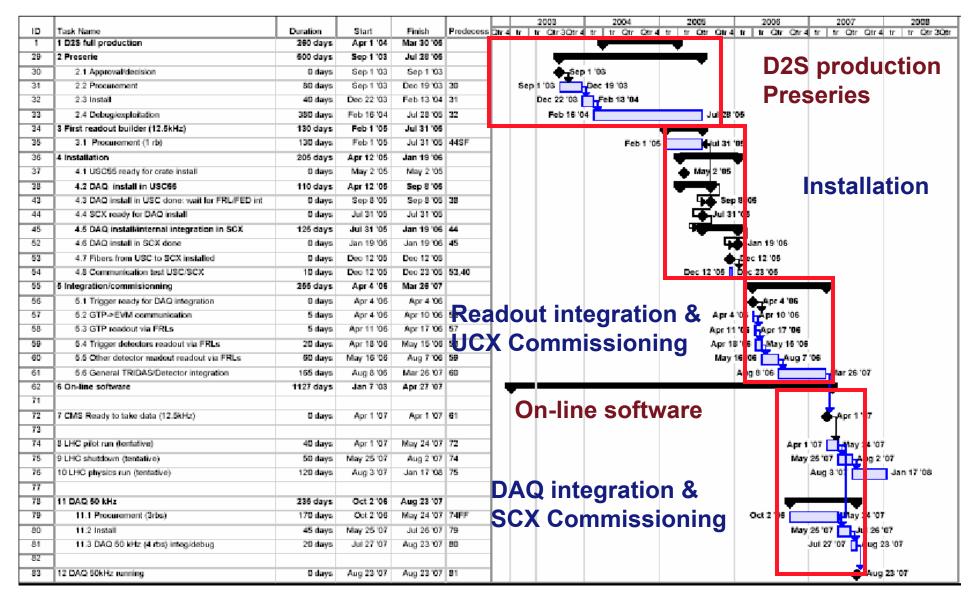

### **DAQ** raw schedule

### 2004 P5 green barrack: Pre-series RB

- -32 GII-FED emulators

- -64 FRLs

- -13 Water cooled racks

- -93 PC dual-CPU

- -D2S Myrinet equipment

- -Readout Builder Myrinet

- -16 PC Filter Farm

### Preseries integration programme

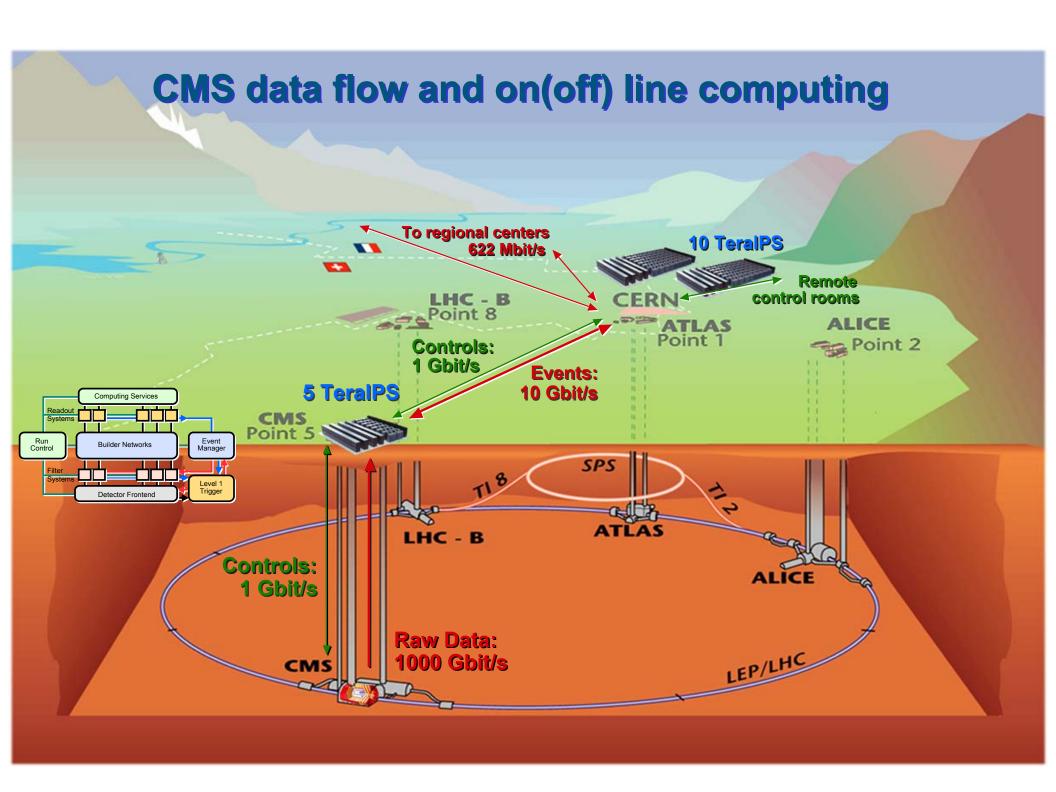

### DAQ data flow and computing model

### Summary design principles

Invest in the advance of communication and processing technologies

Computing (100 kHz Readout, HLT by PC farms)

Communication (Terabit/s networks, GB/s memories)

- Maximally scaling architecture

Exploit technology evolution

Cost optimization via staged installation

**Modular system** (simpler controls, error handling, smaller basic units)

Rely on hardware and software industry standards

Custom/standards (PCI, Ethernet, C++, JAVA, http, XML,..)

### **Conclusions**

The CMS design fulfils the major requirements:

- √100 KHz level-1 readout

- **✓ Event builder:**

- a scalable structure that can go up to 1 Terabit/s

- √ High-Level Trigger by fully programmable processors

- •This design should be considered complete, but not final.

e.g. switches procured in 2008-09 can be different from those of the startup system

- •It is a **system** that is **expected to change** with time, accelerator and experiment conditions. And it has been designed to do so

- •It is conceived to provide the **maximum possible flexibility** to execute a physics selection on-line